# 16-bit Σ-Δ Analog to Digital Converter

#### PRODUCT DESCRIPTION

The MS7705/MS7706 is an analog-to-digital converter for low-frequency measurement. It uses  $\Sigma$ - $\Delta$  conversion technology to realize 16-bit no missing codes feature. The operating voltage range is 2.7V-3.3V or 4.75V-5.25V.

The MS7705/MS7706 is ideal for intelligent, micro-controller, or DSP-based systems. It can set gain, signal polarity and output rate through serial interface. Self-calibration and system calibration can be applied to eliminate gain and offset errors of the system. The typical power dissipation is  $20\mu W$  in standby mode.

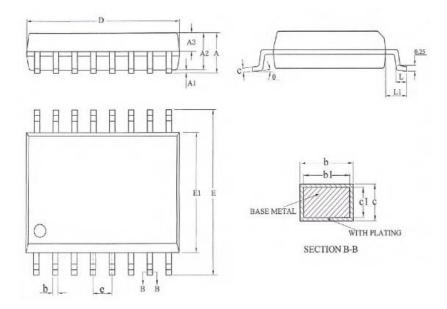

SOW16

#### **FEATURES**

MS7705: Two Fully Differential Input Channels

• MS7706: Three Pseudo Differential Input Channels

• 16-bit No Missing Codes

0.003% Non-linearity

PGA: Gain from 1 to 128

• Serial Port: SPI, QSPI, PMICROWIRE, DSP Compatible

Operating Voltage: 2.7V to 3.3V or 4.75V to 5.25V

Maximum Power Dissipation : 1mW under 3V supply voltage

Maximum Standby Current : 8μA

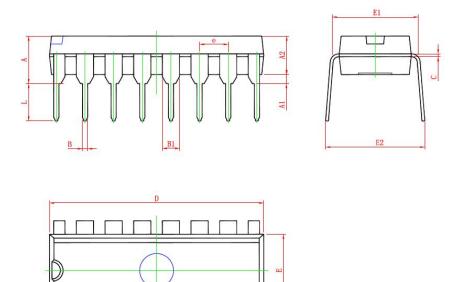

SOW16 and DIP16 Package

DIP16

### **APPLICATIONS**

- Stress Measurement

- Temperature Measurement

- Battery Monitoring

- Smart Transmitter

### **PRODUCT SPECIFICATION**

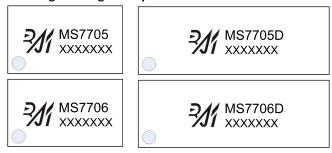

| Part Number | Package | Marking |

|-------------|---------|---------|

| MS7705      | SOW16   | MS7705  |

| MS7705D     | DIP16   | MS7705D |

| *MS7706     | SOW16   | MS7706  |

| *MS7706D    | DIP16   | MS7706D |

VERSION: V1.6

If necessary, please contact Hangzhou Ruimeng Sales Department.

<sup>\*</sup>Don't provide the package temporarily.

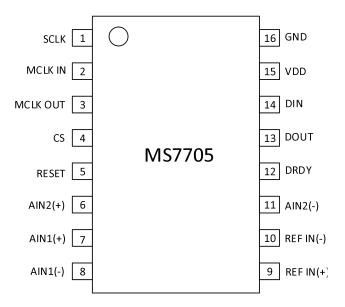

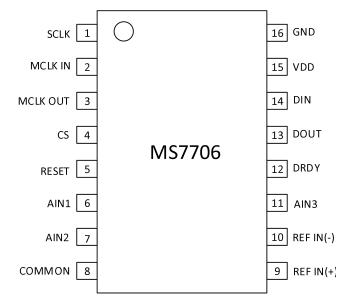

# **PIN CONFIGURATION**

# **PIN DESCRIPTION**

| _   | Na          | me        | _    | _                                                                                                                    |

|-----|-------------|-----------|------|----------------------------------------------------------------------------------------------------------------------|

| Pin | MS7705      | MS7706    | Туре | Description                                                                                                          |

| 1   | SCLK        | SCLK      | ı    | Serial Clock Input                                                                                                   |

|     |             |           |      | Master Clock Signal. It can be provided in the form of crystal / resonator or external clock.                        |

| 2   | MCLK IN     | MCLK IN   | ı    | The crystal / resonator can be connected between MCLK IN and                                                         |

|     |             |           |      | MCLK OUT pins. MCLK IN can also be driven by CMOS compatible                                                         |

|     |             |           |      | clock, but MCLK OUT is not connected.                                                                                |

|     |             |           |      | The clock frequency ranges from 500kHz to 5MHz.                                                                      |

|     |             |           |      | When master clock is crystal / resonator, it is connected between                                                    |

|     |             |           |      | MCLK IN and MCLK OUT pins. If the external clock is connected on                                                     |

| 3   | MCLK        | MCLK      | О    | MCLK IN, the MCLK OUT will provide an inverted clock signal.                                                         |

| 3   | OUT         | OUT       |      | This clock can be used to provide clock source for external circuit                                                  |

|     |             |           |      | and drive a CMOS load.                                                                                               |

|     |             |           |      | MCLK OUT can be turned off by CLKDIS bit in clock register.                                                          |

| 4   | CS          | CS        | I    | Chip Selection, Active Low Logic Input.                                                                              |

| 5   | RESET       | RESET     | I    | Reset Input, Active Low Input.                                                                                       |

|     | A1012/)     | A 13.14   |      | For MS7705, Positive Input of Differential Analog Input Channel 2;                                                   |

| 6   | AIN2(+)     | AIN1      | I    | For MS7706, Input of Analog Input Channel 1.                                                                         |

| _   | A1814 ( . ) | AINIO     |      | For MS7705, Positive Input of Differential Analog Input Channel 1;                                                   |

| 7   | AIN1(+)     | AIN2      | I    | For MS7706, Input of Analog Input Channel 2.                                                                         |

|     |             |           |      | For MS7705, Negative Input of Differential Analog Input Channel 1;                                                   |

| 8   | AIN1(-)     | COMMON    | I    | For MS7706, COMMON Input, Analog Channel 1, 2, 3 Input with                                                          |

|     |             |           |      | reference to the Input Terminal.                                                                                     |

|     |             |           |      | Reference Input Terminal. The reference input is differential and                                                    |

| 9   | REF IN(+)   | REF IN(+) | ı    | requires that REFIN (+) must be more than REFIN (-).                                                                 |

|     |             |           |      | REFIN (+) can be any value between VDD and GND.                                                                      |

| 10  | REF IN(-)   | REF IN(-) | ı    | Reference Input Terminal. REFIN (-) can be any value between VDD and GND, and REFIN (+) must be more than REFIN (-). |

| 11  | AIN2(-)     | AIN3      | ı    | For MS7705, Negative Input of Differential Analog Input Channel 2.  For Ms7706, Input of Analog Input Channel 3.     |

|     | Na     | me     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|--------|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin | MS7705 | MS7706 | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 12  | DRDY   | DRDY   | 0    | Logic Output. The low logic level on this output terminal indicates that the newest results can be obtained from the MS7705/7706 data register. After completing read operation of a complete output word, DRDY immediately returns to high level. If there is no data readout between the two output updates, DRDY will return to high level for 500× tCLKIN before the next update occurs. When DRDY is high level, it can not read data, for fear that data in the data register is read when it is updating. After data is updated, DRDY returns to low level. DRDY is also used to indicate when the MS7705/7706 has completed the on-chip calibration sequence. |

| 13  | DOUT   | DOUT   | 0    | Serial Data Output Terminal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 14  | DIN    | DIN    | ı    | Serial Data Input Terminal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 15  | VDD    | VDD    | Р    | Power Supply, + 2.7V to + 5.25V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 16  | GND    | GND    | -    | Ground Reference Point of Internal Circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

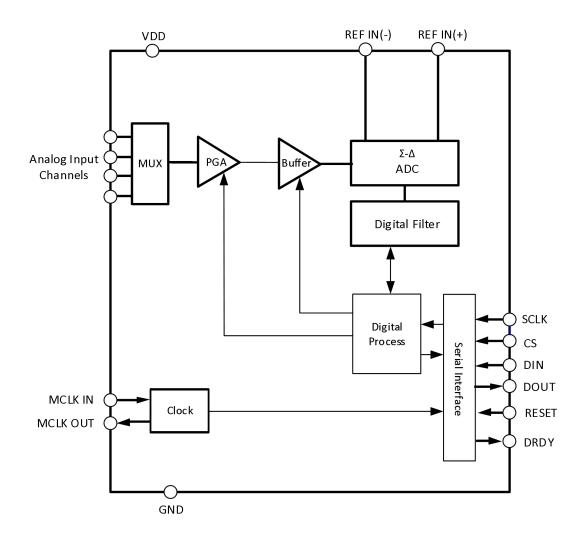

# **BLOCK DIAGRAM**

### **ABSOLUTE MAXIMUM RATINGS**

Any exceeding absolute maximum rating application causes permanent damage to device. Because long-time absolute operation state affects device reliability. The absolute ratings just conclude from a series of extreme tests. It doesn't represent chip can operate normally in these extreme conditions.

| Parameter                | Symbol           | Range             | Unit     |

|--------------------------|------------------|-------------------|----------|

| Power Supply             | VDD              | -0.3 ~ +7.0       | <b>\</b> |

| Analog Input Voltage     | VIN              | -0.3 ~ VDD+0.3    | \<br>\   |

| Reference Input Voltage  | V <sub>REF</sub> | -0.3 ~ VDD+0.3    | V        |

| Digital Input Voltage    | V <sub>DIN</sub> | -0.3 ~ VDD+0.3    | V        |

| Digital Output Voltage   | V <sub>OUT</sub> | -0.3 ~ VDD+0.3    | V        |

| Operating Temperature    | TA               | -40 ~ 85          | °C       |

| Storage Temperature      | T <sub>stg</sub> | -60 ∼ <b>1</b> 50 | °C       |

| Lead Temperature(10s)    |                  | 260               | °C       |

| Electrostatic Protection | ESD              | >4000             | V        |

# **ELECTRICAL CHARACTERISTICS**

Unless otherwise noted, VDD=3V,5V or 2.5V, REF(+)=1.225V, REF(-)=GND, MCLK IN=2.4576MHz.

| Parameter                          | Symbol       | Condition                                | Min         | Тур         | Max    | Unit           |

|------------------------------------|--------------|------------------------------------------|-------------|-------------|--------|----------------|

|                                    |              | Static Characteristic                    |             | Г           | 1      | T              |

| No Missing Codes                   |              |                                          |             | 16          |        | Bits Min       |

| Output Noise                       |              |                                          | See Ta      | ble 2 and 1 | able 4 |                |

| Integral Nonlinearity <sup>1</sup> |              |                                          |             | ±0.003      |        | %of FSR<br>MAX |

| Unipolar Offset Error <sup>2</sup> |              |                                          |             |             |        |                |

| Unipolar Offset Drift <sup>3</sup> |              |                                          |             | 0.5         |        | μV/°C          |

| Bipolar Offset Error <sup>2</sup>  |              |                                          |             |             |        |                |

| Discolor Officet Duift 3           |              | Gain=1~4                                 |             | 0.5         |        | /00            |

| Bipolar Offset Drift <sup>3</sup>  |              | Gain=8~128                               |             | 0.1         |        | μV/°C          |

|                                    | F            | Positive Full-Scale Error <sup>2,4</sup> | 1           | Í           | 1      | ı              |

| Full-Scale Drift 3,5               |              |                                          |             | 0.5         |        | μV/°C          |

| Gain Error <sup>2,6</sup>          |              |                                          |             |             |        |                |

| Gain Drift <sup>3,7</sup>          |              |                                          |             | 0.5         |        | ppm of         |

|                                    |              |                                          |             |             |        | FSR/°C         |

|                                    |              | Negative Full-Scale Error                |             |             |        |                |

| Bipolar Negative                   |              |                                          |             | ±0.001      | ±0.003 | %of FSR        |

| Full-Scale Error <sup>1</sup>      |              |                                          |             |             |        |                |

| Bipolar Negative                   |              | Gain=1~4                                 |             | 1           |        | μV/°C          |

| Full-Scale Drift <sup>3</sup>      |              | Gain=8~128                               |             | 0.6         |        | μV/°C          |

| Analog Inp                         | <del>-</del> | e Input (if not specified, O             | nly for AIN |             | N)<br> |                |

|                                    | CMR          | VDD=5V, Gain=1                           |             | 96          |        |                |

|                                    |              | VDD=5V, Gain=2                           |             | 105         |        |                |

|                                    |              | VDD=5V, Gain=4                           |             | 110         |        |                |

| <br>  Common-mode Rejection 1      |              | VDD=5V, Gain=8~128                       |             | 130         |        | dB             |

| Common-mode Rejection              |              | VDD=3V, Gain=1                           |             | 105         |        |                |

|                                    |              | VDD=3V, Gain=2                           |             | 110         |        |                |

|                                    |              | VDD=3V, Gain=4                           |             | 120         |        |                |

|                                    |              | VDD=3V, Gain=8~128                       |             | 130         |        |                |

| Parameter                                         | Symbol | Condition                                               | Min      | Тур                                                                   | Max      | Unit |

|---------------------------------------------------|--------|---------------------------------------------------------|----------|-----------------------------------------------------------------------|----------|------|

|                                                   |        | Filter Notches 25Hz,50Hz,<br>±0.02 × f <sub>NOTCH</sub> |          | 98                                                                    |          | dB   |

| Normal-mode                                       |        | Filter Notches 20Hz,60Hz,<br>±0.02 × f <sub>NOTCH</sub> |          | 98                                                                    |          | dB   |

| 50 Hz Rejection <sup>1</sup>                      |        | Filter Notches 25Hz,50Hz,<br>±0.02 × f <sub>NOTCH</sub> |          | 150                                                                   |          | dB   |

|                                                   |        | Filter Notches 20Hz,60Hz,<br>±0.02 × f <sub>NOTCH</sub> |          | 150                                                                   |          | dB   |

| Absolute/Common-mode                              |        |                                                         | GND      |                                                                       | VDD      | V    |

| Absolute/Common-mode AIN Voltage <sup>1,8,9</sup> |        | Register Bit BUF=0                                      | GND-0.1  |                                                                       | VDD+0.03 | V    |

| Absolute/Common-mode  AIN Voltage <sup>1,8</sup>  |        | Register Bit BUF =1                                     | GND+0.05 |                                                                       | VDD-1.5  | V    |

| AIN DC Input Current <sup>1</sup>                 |        |                                                         |          |                                                                       | 1        | nA   |

| AIN Sample Capacitance <sup>1</sup>               |        |                                                         |          |                                                                       | 10       | pF   |

| AIN Differential Voltage <sup>10</sup>            |        | Register Bit BUF =1 Register Bit BUF =0                 |          | 0 to +V <sub>REF</sub> /Gain<br>±V <sub>REF</sub> /Gain <sup>11</sup> |          | V    |

| AIN Input Sample Rate                             | fs     |                                                         |          | Gain×f <sub>CLKIN</sub> /64<br>f <sub>CLKIN</sub> /8                  |          | MHz  |

|                                                   |        | VDD=2.7~3.3V<br>V <sub>REF</sub> =1.225±1%              | 1        |                                                                       | 1.75     |      |

| Reference Input Range                             |        | VDD=4.75~5.25V<br>V <sub>REF</sub> =2.5±1%              | 1        |                                                                       | 3.5      | V    |

| REF IN Input Sample Rate                          |        |                                                         |          | f <sub>CLKIN</sub> /64                                                |          | MHz  |

|                                                   |        | Logic Input                                             |          |                                                                       |          |      |

| Input Current                                     |        | All Inputs  Except MCLK IN                              |          | ±1nA                                                                  | ±1μA     | μΑ   |

|                                                   |        | MCLK IN                                                 |          | ±2                                                                    | ±10      |      |

|                                             |                                   | T                                                                    | 1                            |   | 1                              |    |

|---------------------------------------------|-----------------------------------|----------------------------------------------------------------------|------------------------------|---|--------------------------------|----|

| Input Low Voltage,                          | .,,                               | VDD=5V                                                               |                              |   | 0.8                            | W  |

| Except SCLK and MCLK IN                     | V <sub>INL</sub>                  | VDD=3V                                                               |                              |   | 0.4                            | V  |

| Input High Voltage, Except SCLK and MCLK IN | V <sub>INH</sub>                  | VDD=3 or 5V                                                          | 2.0                          |   |                                | ٧  |

|                                             | V <sub>T+</sub>                   |                                                                      | 1.4                          |   | 3                              |    |

|                                             | V <sub>T-</sub>                   | VDD=5V                                                               | 0.8                          |   | 1.4                            |    |

|                                             | V <sub>T+</sub> - V <sub>T-</sub> |                                                                      | 0.4                          |   | 0.8                            |    |

| SCLK Input Voltage                          | V <sub>T+</sub>                   |                                                                      | 1                            |   | 2                              | V  |

|                                             | V <sub>T-</sub>                   | VDD=3V                                                               | 0.4                          |   | 1.1                            |    |

|                                             | V <sub>T+</sub> - V <sub>T-</sub> |                                                                      | 0.375                        |   | 0.8                            |    |

| _                                           |                                   | VDD=5V                                                               |                              |   | 0.8                            |    |

| MCLK IN Low Voltage                         |                                   | VDD=3V                                                               |                              |   | 0.4                            | V  |

|                                             | ı                                 | .ogic Output (including I                                            | MCLK OUT)                    |   |                                |    |

| Outout Law Valtage                          |                                   | VDD=5V,I <sub>SINK</sub> =800μA<br>(Except MCLK OUT) <sup>12</sup>   |                              |   | 0.4                            | V  |

| Output Low Voltage                          |                                   | VDD=3V,I <sub>SINK</sub> =100μA<br>(Except MCLK OUT) <sup>12</sup>   |                              |   | 0.4                            | V  |

|                                             |                                   | VDD=5V,I <sub>SOURCE</sub> =200μA<br>(Except MCLK OUT) <sup>12</sup> | 4                            |   |                                | ,  |

| Output High Voltage                         |                                   | VDD=3V,I <sub>SOURCE</sub> =100μA<br>(Except MCLK OUT) <sup>12</sup> | VDD-0.6                      |   |                                | V  |

| Leakage Current, Floating State             |                                   |                                                                      |                              |   | ±10                            | μΑ |

| Output Capacitance, Floating State 13       |                                   |                                                                      |                              | 9 |                                | pF |

| Data Output Code                            |                                   | Unipolar Mode Bipolar Mode                                           | Binary Offset Binary         |   |                                |    |

|                                             |                                   | System Calibrati                                                     |                              |   |                                |    |

| Positive Full-Scale Limit 14                |                                   | Gain=1~128                                                           |                              |   | (1.05×V <sub>REF</sub> )/Gain  | ٧  |

| Negative Full-Scale Limit 14                |                                   | Gain=1~128                                                           |                              |   | -(1.05×V <sub>REF</sub> )/Gain | V  |

| Offset Limit 14                             |                                   | Gain=1~128                                                           |                              |   | -(1.05×V <sub>REF</sub> )/Gain | >  |

| Input Range <sup>15</sup>                   |                                   | Gain=1~128                                                           | (0.8×V <sub>REF</sub> )/Gain |   | (2.1×V <sub>REF</sub> )/Gain   | ٧  |

| Parameter                                                                      | Symbol                                        | Condition                                       | Min | Тур | Max  | Unit |  |  |

|--------------------------------------------------------------------------------|-----------------------------------------------|-------------------------------------------------|-----|-----|------|------|--|--|

| Power Dissipation (Apply External Clock , CLKDIS =1, Digital I/Ps = 0V or VDD) |                                               |                                                 |     |     |      |      |  |  |

| VDD=2.7~3.3V                                                                   |                                               |                                                 |     |     |      |      |  |  |

|                                                                                |                                               | BUF=0,f <sub>CLKIN</sub> =1MHz, Gain=1~128      |     |     | 0.32 |      |  |  |

|                                                                                |                                               | BUF=1,f <sub>CLKIN</sub> =1MHz, Gain=1~128      |     |     | 0.6  |      |  |  |

| Power Supply Current <sup>16</sup>                                             |                                               | BUF=0,f <sub>CLKIN</sub> =2.4576MHz, Gain=1~4   |     |     | 0.4  |      |  |  |

|                                                                                | I <sub>DD</sub>                               | BUF=0,f <sub>CLKIN</sub> =2.4576MHz, Gain=8~128 |     |     | 0.6  | mA   |  |  |

|                                                                                | BUF=1,f <sub>CLKIN</sub> =2.4576MHz, Gain=1~4 |                                                 |     |     | 0.7  |      |  |  |

|                                                                                |                                               | BUF=1,f <sub>CLKIN</sub> =2.4576MHz, Gain=8~128 |     |     | 1.1  |      |  |  |

|                                                                                |                                               | VDD=4.75~5.25\                                  | /   |     |      |      |  |  |

|                                                                                |                                               | BUF=0,f <sub>CLKIN</sub> =1MHz, Gain=1~128      |     |     | 0.45 |      |  |  |

|                                                                                |                                               | BUF=1,f <sub>CLKIN</sub> =1MHz, Gain=1~128      |     |     | 0.7  |      |  |  |

| Power Supply Current 16                                                        |                                               | BUF=0,f <sub>CLKIN</sub> =2.4576MHz, Gain=1~4   |     |     | 0.6  | mA   |  |  |

|                                                                                | l <sub>DD</sub>                               | BUF=0,f <sub>CLKIN</sub> =2.4576MHz, Gain=8~128 |     |     | 0.85 |      |  |  |

|                                                                                |                                               | BUF=1,f <sub>CLKIN</sub> =2.4576MHz, Gain=1~4   |     |     | 0.9  |      |  |  |

|                                                                                |                                               | BUF=1,f <sub>CLKIN</sub> =2.4576MHz, Gain=8~128 |     |     | 1.3  |      |  |  |

|                                                                                |                                               | MCLK IN = 0 V or VDD, VDD = 3 V                 |     | 8   |      | uA   |  |  |

| Standby Power Dissipation <sup>17</sup>                                        |                                               | MCLK IN = 0 V or VDD, VDD = 5 V                 |     | 16  |      |      |  |  |

| Power Supply Rejection <sup>18,19</sup>                                        |                                               |                                                 |     |     |      | dB   |  |  |

- 1. These data has been determined at initial design.

- 2. Calibration is one conversion, Table 2 and Table 4 show these noise error. This is suitable for after calibration under expected temperature.

- 3. These drift error would be eliminated after re-calibration under any temperature.

- 4. Full-scale error includes zero-scale error (unbipolar drift error or bipolar zero-scale error ) and it is applicable for unbipolar and bipolar input ranges.

- 5. Full-scale drift includes zero-scale drift (unbipolar offset drift or bipolar zero-scale drift). It is applicable for unbipolar and bipolar input ranges.

- 6. Gain error doesn't include zero-scale error. The calculation method : unbipolar range (full-scale error-unbipolar offset error); bipolar range (full-scale error-bipolar zero-scale error).

- 7. Gain drift doesn't include unbipolar offset drift and bipolar zero-scale drift. When zero-scale calibration is executed, gain drift is the system drift value.

- 8. Common-mode voltage range: analog input voltage (GND-100mV) to (VDD+30mV).

- 9. The analog input voltage of the MS7705/7706 can low to GND-200mV, but leakage current would be increased.

- 10. The voltage range on AIN(+) is respective to AIN(-) terminal for the MS7705, COMMON terminal for the MS7706 .

- 11.  $V_{REF} = REF IN(+) REF IN(-)$ .

- 12. Only when one CMOS load is loaded, these logic output levels are applicable for MCLK OUT.

- 13. Test sample at +25°C to ensure consistency.

- 14. After calibration, if analog input is more than positive full-scale, converter would output all 1; if less than negative full-scale, converter would output all 0.

- 15. Calibration voltage limit shouldn't more than VDD+30mV or less than GND-100mV applied on analog input terminal. Offset calibration limit is suitable for unbipolar point and bipolar zero point.

- 16. When use crystal or ceramic oscillator as clock source of MCLK, the current and power dissipation of VDD depend on the type of crystal and ceramic oscillator (see "clock and oscillator").

- 17. In standby mode, if external master clock works continuously, the typical value of standby current would increase to  $150\mu(VDD=5V)$  or  $75\mu A(VDD=3V)$ . When use crystal or ceramic oscillator as clock source, internal oscillator would work continuously work in standby mode, and the power supply current would vary with the type of crystal and ceramic oscillator (see "standby mode").

- 18. The measurement in DC only apply to the selected passband frequency. PSRR exceeds 120dB at 50Hz (filter notch is 25Hz or 50Hz ). PSRR exceeds 120dB at 60Hz (filter notch is 20Hz or 60Hz ).

19. PSRR is decided by gain and power as follows

| Gain   | 1  | 2  | 4  | 8~28 |

|--------|----|----|----|------|

| VDD=3V | 86 | 78 | 85 | 93   |

| VDD=5V | 90 | 78 | 84 | 91   |

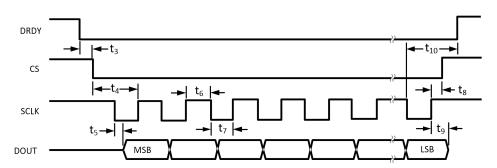

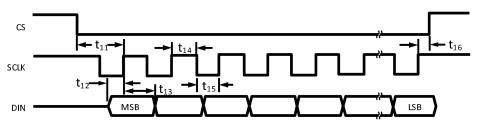

### **TIMING CHARACTERISTICS**

If there is no special description, VDD=2.7 to 5.25V, GND=0V; fCLKIN=2.4576MHz, input logic low is 0V, input logic high is VDD.Test at 25°C. All input signals meet tR=tF =5ns (10% to 90% of VDD) and start timing from 1.6V. See Figure 1 and Figure 2.

Table 1. Timing Characteristic <sup>1,2</sup>

| Parameter                                          | Symbol              | Condition     | Min                    | Тур                    | Max | Unit |

|----------------------------------------------------|---------------------|---------------|------------------------|------------------------|-----|------|

| Master Clock Frequency 3,4                         | fCLKIN              |               | 0.4                    |                        | 2.5 | MHz  |

| Master Clock Cycle                                 | <sup>t</sup> CLKIN  |               | 2500                   |                        | 400 | ns   |

| Master Clock Low Level Time                        | <sup>t</sup> CLK LO |               | 0.4×t <sub>CLKIN</sub> |                        |     | ns   |

| Master Clock High Level Time                       | <sup>t</sup> CLK HI |               | 0.4×t <sub>CLKIN</sub> |                        |     | ns   |

| CS High Level Time                                 | t1                  |               |                        | 500×t <sub>CLKIN</sub> |     | ns   |

| RESET Pulse Width                                  | t2                  |               | 100                    |                        |     | ns   |

|                                                    | Re                  | ad Operation  |                        |                        |     |      |

| DRDY to CS Setup Time                              | t3                  |               | 0                      |                        |     |      |

| CS Falling Edge to SCLK Rising Edge Setup Time     | t4                  |               | 120                    |                        |     | ns   |

| SCLK Falling Edge to Data                          | _                   | VDD=5V        | 0                      |                        | 80  |      |

| Valid Delay <sup>5</sup>                           | t5                  | VDD=3V        | 0                      |                        | 100 | ns   |

| SCLK High Pulse Width                              | t6                  |               | 100                    |                        |     | ns   |

| SCLK Low Pulse Width                               | t7                  |               | 100                    |                        |     | ns   |

| CS Rising Edge to SCLK Rising Edge Holding Time    | t8                  |               | 0                      |                        |     | ns   |

| Bus Release Time                                   |                     | VDD=5V        | 10                     |                        | 60  |      |

| after SCLK Rising Edge <sup>6</sup>                | t9                  | VDD=3V        | 10                     |                        | 100 | ns   |

| SCLK Falling Edge to  DRDY High Level <sup>7</sup> | t10                 |               |                        |                        | 100 | ns   |

|                                                    | Wr                  | ite Operation | 1                      |                        |     |      |

| CS Falling Edge to SCLK Rising Edge<br>Setup Time  | t11                 |               | 120                    |                        |     | ns   |

| Data Valid to SCLK Rising Edge<br>Setup Time       | t12                 |               | 30                     |                        |     | ns   |

| Data Valid to SCLK Falling Edge<br>Setup Time      | t13                 |               | 20                     |                        |     | ns   |

| SCLK High Pulse Width                              | t14                 |               | 100                    |                        |     | ns   |

| SCLK Low Pulse Width                               | t15                 |               | 100                    |                        |     | ns   |

| CS Rising Edge to SCLK Rising Edge<br>Holding Time | t16                 |               | 0                      |                        |     | ns   |

- 1. Test at 25°C. All input signals meet:  $t_R = t_F = 5$ ns (VDD 10%~90%), start timing from 1.6V.

- 2. See Figure 7 and Figure 8.

- 3. fCLKIN duty cycle is 45%~55%. As long as the MS7705/7706 is not in standby mode, fCLKIN must be provided. If clock is not provided, the device would extract higher current more than rating value and may become uncalibrated.

- 4. When the MS7705/7706 in manufacture test, use f<sub>CLKIN</sub>=2.4576MHz (1MHz is used for some tests of I<sub>DD</sub>) to ensure that device operates at 400kHz.

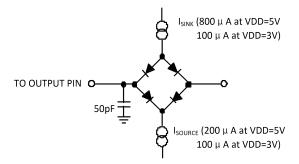

- 5. These values are measured in load shown in Figure 1. It is defined that the time required for output crossing Vol or VoH.

- 6. These values are measured when data output is 0.5V (load situation is shown in Figure 1). Then backstep by measured data to remove the effect of charging and discharging 50pF capacitor. It indicates all time values in parameter table are real bus release time and are independent of external load capacitors.

- 7. After result data is updated, DRDY returns high level after the first read. When DRDY is high level, read operation can be performed again. However, it is noted that following read operations couldn't too close to next update.

Figure 1. Load Circuit (excess time and bus release time)

### **OUTPUT NOISE**

Table 2 and 4 show the output noise (RMS) of MS7705/7706 at the selectable notch and -3dB frequencies, selected by the clock registers FSO and FS1. Data is at bipolar input, VREF=+2.5V/1.225, VDD=5V/3V. These values are typical values when the device operates in buffered or unbuffered mode and the analog input voltage is 0V.

Table 3 and Table 5 show the peak to peak output noise. Note that the resolution represented by these numbers is not code blinking. These values apply to the bipolar input range in buffered and unbuffered modes (VREF = +2.5V/+1.225). These values are typical and close to the nearest LSB. It's required that CLKDIV bit of clock register is set 0.

Table 2. Output Noise VS. Gain and Output Rate @ 5V

|               |           |        | z. oatpat | 110.50 15.  | ouiii uiiu c | output Nate | <u></u> |         |          |

|---------------|-----------|--------|-----------|-------------|--------------|-------------|---------|---------|----------|

| Filter Notch  |           |        |           |             |              |             |         |         |          |

| and Data Rate | -3dB Freq | Gain=1 | Gain=2    | Gain=4      | Gain=8       | Gain=16     | Gain=32 | Gain=64 | Gain=128 |

|               |           |        | М         | CLK IN = 2. | 4576MHz      |             |         |         |          |

| 50Hz          | 13.1Hz    | 4.1    | 2.1       | 1.2         | 0.75         | 0.7         | 0.66    | 0.63    | 0.6      |

| 60Hz          | 15.72Hz   | 5.1    | 2.5       | 1.4         | 0.8          | 0.75        | 0.7     | 0.67    | 0.62     |

| 250Hz         | 65.5Hz    | 110    | 49        | 31          | 17           | 8           | 3.6     | 2.3     | 1.7      |

| 500Hz         | 131Hz     | 550    | 285       | 145         | 70           | 41          | 22      | 9.1     | 4.7      |

|               | ,         |        |           | MCLK IN =   | = 1MHz       |             |         |         |          |

| 20Hz          | 5.24Hz    | 4.1    | 2.1       | 1.2         | 0.75         | 0.7         | 0.66    | 0.63    | 0.6      |

| 25Hz          | 6.55Hz    | 5.1    | 2.5       | 1.4         | 0.8          | 0.75        | 0.7     | 0.67    | 0.62     |

| 100Hz         | 26.2Hz    | 110    | 49        | 31          | 17           | 8           | 3.6     | 2.3     | 1.7      |

| 200Hz         | 52.4Hz    | 550    | 285       | 145         | 70           | 41          | 22      | 9.1     | 4.7      |

Table 3. Effective Bits VS. Gain and Output Rate @5V

|                 |           |        |        |             |         | o e p a e ma e e |         |         |          |

|-----------------|-----------|--------|--------|-------------|---------|------------------|---------|---------|----------|

| Filter Trap and |           |        |        |             |         |                  |         | ī       |          |

| Data Rate       | -3dB Freq | Gain=1 | Gain=2 | Gain=4      | Gain=8  | Gain=16          | Gain=32 | Gain=64 | Gain=128 |

|                 |           |        | M      | CLK IN = 2. | 4576MHz |                  |         |         |          |

| 50Hz            | 13.1Hz    | 16     | 16     | 16          | 16      | 16               | 16      | 15      | 14       |

| 60Hz            | 15.72Hz   | 16     | 16     | 16          | 16      | 15               | 14      | 14      | 13       |

| 250Hz           | 65.5Hz    | 13     | 13     | 13          | 13      | 13               | 13      | 12      | 12       |

| 500Hz           | 131Hz     | 10     | 10     | 10          | 10      | 10               | 10      | 10      | 10       |

|       |        |    |    | MCLK IN = | = 1MHz |    |    |    |    |

|-------|--------|----|----|-----------|--------|----|----|----|----|

| 20Hz  | 5.24Hz | 16 | 16 | 16        | 16     | 16 | 16 | 15 | 14 |

| 25Hz  | 6.55Hz | 16 | 16 | 16        | 16     | 15 | 14 | 14 | 13 |

| 100Hz | 26.2Hz | 13 | 13 | 13        | 13     | 13 | 13 | 12 | 12 |

| 200Hz | 52.4Hz | 10 | 10 | 10        | 10     | 10 | 10 | 10 | 10 |

Table 4. Output Noise VS. Gain and Output Rate @ 3V

|               |           |        |        |             |         | acpat mate |         |         |          |

|---------------|-----------|--------|--------|-------------|---------|------------|---------|---------|----------|

| Filter Notch  |           |        |        |             |         |            |         |         |          |

| and Data Rate | -3dB Freq | Gain=1 | Gain=2 | Gain=4      | Gain=8  | Gain=16    | Gain=32 | Gain=64 | Gain=128 |

|               |           |        | M      | CLK IN = 2. | 4576MHz |            |         |         |          |

| 50Hz          | 13.1Hz    | 3.8    | 2.4    | 1.5         | 1.3     | 1.1        | 1.0     | 0.9     | 0.9      |

| 60Hz          | 15.72Hz   | 5.1    | 2.9    | 1.7         | 1.5     | 1.2        | 1.0     | 0.9     | 0.9      |

| 250Hz         | 65.5Hz    | 50     | 25     | 14          | 9.9     | 5.1        | 2.6     | 2.3     | 2.0      |

| 500Hz         | 131Hz     | 270    | 135    | 65          | 41      | 22         | 9.7     | 5.1     | 3.3      |

|               |           |        |        | MCLK IN =   | = 1MHz  |            |         |         |          |

| 20Hz          | 5.24Hz    | 3.8    | 2.4    | 1.5         | 1.3     | 1.1        | 1.0     | 0.9     | 0.9      |

| 25Hz          | 6.55Hz    | 5.1    | 2.9    | 1.7         | 1.5     | 1.2        | 1.0     | 0.9     | 0.9      |

| 100Hz         | 26.2Hz    | 50     | 25     | 14          | 9.9     | 5.1        | 2.6     | 2.3     | 2.0      |

| 100H2         | 20.202    | 30     |        | 14          | 9.9     | ٥.1        | 2.0     | 2.3     | 2.0      |

| 200Hz         | 52.4Hz    | 270    | 135    | 65          | 41      | 22         | 9.7     | 5.1     | 3.3      |

Table 5. Effective Bits VS. Gain and Output Rate @3V

| Filter Trap and |           |        |        |              |           |              |         |         |          |

|-----------------|-----------|--------|--------|--------------|-----------|--------------|---------|---------|----------|

| Data Rate       | -3dB Freq | Gain=1 | Gain=2 | Gain=4       | Gain=8    | Gain=16      | Gain=32 | Gain=64 | Gain=128 |

|                 |           |        | M      | CLK IN = 2.  | 4576MHz   |              |         |         |          |

| 50Hz            | 13.1Hz    | 16     | 16     | 15           | 15        | 14           | 13      | 13      | 12       |

| 60Hz            | 15.72Hz   | 16     | 16     | 15           | 14        | 14           | 13      | 13      | 12       |

| 250Hz           | 65.5Hz    | 13     | 13     | 13           | 13        | 12           | 12      | 11      | 11       |

| 500Hz           | 131Hz     | 10     | 10     | 10           | 10        | 10           | 10      | 10      | 10       |

| 300112          | 131112    |        |        | MCLK IN =    | ı         | 10           |         | 1 10    | 1 20     |

|                 | 1         |        |        | IVICER IIV - | - 1141117 |              |         |         | 1        |

| 20Hz            | 5.24Hz    | 16     | 16     | 15           | 15        | 14           | 13      | 13      | 12       |

| 25Hz            | 6.55Hz    | 16     | 16     | 15           | 14        | 14           | 13      | 13      | 12       |

| 100Hz           | 26.2Hz    | 13     | 13     | 13           | 13        | 12           | 12      | 11      | 11       |

| 200112          | 23.2112   |        |        |              |           | <del>_</del> |         |         |          |

| 200Hz           | 52.4Hz    | 10     | 10     | 10           | 10        | 10           | 10      | 10      | 10       |

### **FUNCTIONAL DESCRIPTION**

### **On-chip Register**

The MS7705/7706 contains registers (communication register, setting register, clock register, data register, test register, zero-scale calibration register, full-scale calibration register), which are accessed through serial ports of the device.

#### Communication Register (RS2, RS1, RS0=0, 0, 0)

Communication register is an 8-bit register, which can read and write data. The data written determines which register the next read or write occurs on. Once the next read or write operation is completed on the selected register, the interface returns to the communication register to receive a write operation. This is interface default state. After power on or reset, the MS7705/7706 is in this default state, waiting for a write operation to the communication register. Under the condition of lost interface sequence, if write operation at DIN level persists for a long time (at least 32 serial clock cycles), MS7705/7706 will go back to default state.

Table 6. Communication Register

| Bit  | 7         | 6      | 5      | 4      | 3      | 2       | 1      | 0      |

|------|-----------|--------|--------|--------|--------|---------|--------|--------|

| Name | 0/DRDY(0) | RS2(0) | RS1(0) | RS0(0) | R/W(0) | STBY(0) | CH1(0) | CH0(0) |

Note: The content in bracket is the default value of power on reset.

Table 7. Function Description of Each Bit in Communication Register

| Register | Description                                                                                           |

|----------|-------------------------------------------------------------------------------------------------------|

|          | To write to the communication register, a "0" must be written to this one. If "1" is written to       |

|          | this, subsequent bits will not be able to write to the register. It will stay in this bit until a "0" |

| 0/DRDY   | is written to it, and the next seven bits will be loaded into the communication register. For         |

|          | read operation, this bit provides DRDY flag of the device. The state of the bit is the same as        |

|          | the state of DRDY output pin.                                                                         |

| RS2-RS0  | Register Select Bit. These three bits choose which register to read / write next.                     |

| R/W      | Read / Write Selection. "0" indicates that the next operation is write, and "1" indicates that        |

| K/VV     | the next operation is read.                                                                           |

|          | Standby Mode. If "1" is written to this bit, it is in wait or power down mode. In this mode,          |

| STBY     | the power supply current consumed by the device is only 10 μA. In standby mode, the device            |

| 3181     | will maintain its calibration coefficient and control word information. Write "0" and the             |

|          | device is in normal operation mode.                                                                   |

|          | Channel Selection. These two bits select a channel for data conversion or access calibration          |

|          | coefficient, as shown in Table 9. Three pairs of calibration registers in the device are used to      |

|          | store the calibration coefficients. Table 9 and Table 10 indicate which channel combinations          |

| CU1 CU0  | have independent calibration coefficients. When CH1 is logic 1 and CH0 is logic 0, AIN (-)            |

| CH1, CH0 | /COMMON input pin of MS7705/7706 is shorted to itself respectively. This can be used as a             |

|          | test method to evaluate the noise performance (without external noise source). In this                |

|          | mode, the AIN1 (-) /COMMON input terminal must be connected to an external voltage and                |

|          | within the allowable common mode voltage range.                                                       |

| Table 8. | Register | Selection |

|----------|----------|-----------|

|----------|----------|-----------|

| RS2 | RS1 | RS0 | Register               | Register bits |

|-----|-----|-----|------------------------|---------------|

| 0   | 0   | 0   | Communication Register | 8 bits        |

| 0   | 0   | 1   | Setting Register       | 8 bits        |

| 0   | 1   | 0   | Clock Register         | 8 bits        |

| 0   | 1   | 1   | Data Register          | 16 bits       |

| 1   | 0   | 0   | Test Register          | 8 bits        |

| 1   | 0   | 1   | None                   |               |

| 1   | 1   | 0   | Offset Register        | 24 bits       |

| 1   | 1   | 1   | Gain Register          | 24 bits       |

### Table 9. MS7705 Input Channel Selection

| CH1 | CH0 | AIN(+)  | AIN(-)  | Calibration Register Pair |

|-----|-----|---------|---------|---------------------------|

| 0   | 0   | AIN1(+) | AIN1(-) | Register Pair 0           |

| 0   | 1   | AIN2(+) | AIN2(-) | Register Pair 1           |

| 1   | 0   | AIN1(-) | AIN1(-) | Register Pair 0           |

| 1   | 1   | AIN1(-) | AIN2(-) | Register Pair2            |

# Table 10. MS7706 Input Channel Selection

| CH1 | CH0 | AIN    | Reference | Calibration Register Pair |

|-----|-----|--------|-----------|---------------------------|

| 0   | 0   | AIN1   | COMMON    | Register Pair 0           |

| 0   | 1   | AIN2   | COMMON    | Register Pair 1           |

| 1   | 0   | COMMON | COMMON    | Register Pair 0           |

| 1   | 1   | AIN3   | COMMON    | Register Pair 2           |

# Setting Register (RS2, RS1, RS0 = 0, 0, 1), Power On / Reset Status: 01Hex

The setting register is an 8-bit register, which can read and write data.

# Table 11. Setting Register

| Bit  | 7      | 6      | 5     | 4     | 3     | 2      | 1      | 0        |

|------|--------|--------|-------|-------|-------|--------|--------|----------|

| NAME | MD1(0) | MD0(0) | G2(0) | G1(0) | G0(0) | B/U(0) | BUF(0) | FSYNC(1) |

### Table 12. Function Description of Each Bit in Setting Register

| Register | Description                                                                                       |

|----------|---------------------------------------------------------------------------------------------------|

| MD1 MD0  | MSC Operation Mode Control.                                                                       |

| MD1, MD0 | These two bits control the operation mode of MSC, as shown in Table 13.                           |

| G2-G0    | Gain Select Bit. These three bits control the gain of on-chip PGA, as shown in Table 14.          |

| 5/11     | Bipolar / Unipolar Control.                                                                       |

| B/U      | "0" indicates bipolar operation and "1" indicates unipolar operation.                             |

|          | Buffer Control. This bit is "0", the on-chip buffer is short, and the VDD consumption current     |

| BUF      | is reduced. When this bit is "1", the on-chip buffer is connected with analog input, and it       |

|          | can connect to a higher impedance input source.                                                   |

|          | Filter Synchronization. At high level, the node of digital filter, control logic and calibration  |

|          | control logic are in reset state, and the analog modulator is also controlled in reset state. At  |

| FSYNC    | low level, the modulator and filter begin to process data and produce a valid word within 3       |

|          | × (1/output rate) time (i.e. filter setup time). Fsync doesn't affect digital interface and reset |

|          | the DRDY output( if it is low).                                                                   |

Table 13. Operation Mode Selection

| MD1 | MD0 | Operation Mode                                                                                   |

|-----|-----|--------------------------------------------------------------------------------------------------|

| 0   | 0   | Normal Mode. In this mode, the converter performs normal analog-to-digital conversion.           |

|     |     | Self Calibration. Self calibration is activated on the channels selected by CH1 and CH2 in       |

|     |     | the communication register. This is a step calibration. After completing this task, it returns   |

|     |     | to normal mode, that is, MD1 and MD0 are 0. At the beginning of calibration, the DRDY            |

| 0   | 1   | output pin or DRDY bit is high level and returns to low level after calibration. At this time,   |

|     |     | a new valid word is generated in the data register. The zero-scale calibration is performed      |

|     |     | at the input internal short circuit (zero input), and the full-scale calibration is performed at |

|     |     | the selected gain and internally generated VREF / selected gain conditions.                      |

|     |     | Zero-scale System Calibration. Activate zero-scale system calibration on the channel             |

|     |     | selected by CH1 and CH2 in the communication register. When this calibration sequence is         |

|     |     | used, the input voltage on the analog input is calibrated at the selected gain. During           |

| 1   | 0   | calibration, the input voltage should be stable. At the beginning of calibration, DRDY           |

|     |     | outputs or the DRDY bit is high, and the zero-scale system returns to low level after the        |

|     |     | calibration is completed. At this time, a new valid word is generated on the data register.      |

|     |     | At the end of calibration, the device returns to normal mode, that is, MD1 and MD0 are 0.        |

|     |     | Full-scale System Calibration: activates full-scale system calibration on the selected input     |

|     |     | channel. In this calibration sequence, the input voltage on the analog input terminal            |

|     |     | completes the calibration at the selected gain. The input voltage should be stable during        |

| 1   | 1   | calibration. At the beginning of calibration, DRDY outputs or DRDY bit is high level, and        |

|     |     | after the full-scale system calibration is completed, it returns to low level. At this time, a   |

|     |     | new valid word is generated in the data register. At the end of calibration, the device          |

|     |     | returns to normal mode, that is, MD1 and MD0 are 0.                                              |

Table 14. Gain Selection

| G2 | G1 | G0 | Gain |

|----|----|----|------|

| 0  | 0  | 0  | 1    |

| 0  | 0  | 1  | 2    |

| 0  | 1  | 0  | 4    |

| 0  | 1  | 1  | 8    |

| 1  | 0  | 0  | 16   |

| 1  | 0  | 1  | 32   |

| 1  | 1  | 0  | 64   |

| 1  | 1  | 1  | 128  |

# Clock Register (RS2, RS1, RS0 = 0,1,0), Power On / Reset Status: 05Hex

The clock register is an 8-bit register that can read / write data.

### Table 15. Clock Register

| Bit  | 7       | 6       | 5       | 4         | 3         | 2      | 1      | 0      |

|------|---------|---------|---------|-----------|-----------|--------|--------|--------|

| Name | ZERO(0) | ZERO(0) | ZERO(0) | CLKDIS(0) | CLKDIV(0) | CLK(1) | FS1(0) | FS0(0) |

Table 16. Function Description of Each Bit in Clock Register

| Register | Table 16. Function Description of Each Bit in Clock Register  Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ZERO     | Must write 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CLKDIS   | Master Clock Inhibit Bit. Logic "1" prevents the master clock outputting from MCLK OUT pin. When prohibited, MCLK OUT output pin is at low level. This feature enables users to flexibly use MCLK OUT pin. For example, MCLK OUT can be used as the clock source of other devices in the system, or MCLK OUT can be turned off, so that the device has the power saving performance. When an external master clock is connected to MCLK IN, MS7705/7706 keeps the internal clock and performs normal conversion when CLKDIS bit is valid. When a crystal oscillator or a ceramic resonator is connected between MCLK IN and MCLK OUT, so when the CLKDIS bits are valid, the MS7705/7706 clock will stop and no analog-to-digital conversion will be performed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CLKDIV   | Clock Divider Bit. When set to logic 1, the clock frequency at the MCLK IN pin is divided by 2. When set to logic 0, the frequency at the MCLK IN pin is actually the internal frequency of the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CLK      | Clock Bit. CLK bit should be set according to operation frequency of the MS7705/7706. If master clock frequency of converter is 2.4576MHz (CLKDIV=0) or 4.9152MHz (CLKDIV=1), CLK should be set "1". If master clock frequency of the device is 1MHz (CLKDIV== 0) or 2MHz (CLKDIV= 1), this bit should be set "0". This bit sets appropriate scale current for given operation frequency and also selects the output update rate of the device (along with FS1 and FS0). If CLK doesn't set correctly according to master clock frequency, the MS7705/7706 will not be able to achieve the target.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| FS1,FS0  | Filter Select Bit, which together with CLK determine the output update rate of the device. Table 17 shows the first notch and -3dB frequency of the filter. On-chip digital filter generates sinc3 (or (sinx/x)3) filter response. Along with gain select, it also determines the output noise. The change of filter notch and selected gain would have effect on resolution. Table 2 and Table 5 show the filter notch frequency and gain VS. output noise and resolution. The output data rate (or valid conversion time) is equal to the selected frequency of first notch. For example, if the first notch is selected in 50Hz, the output rate of each word is 50Hz, that is, output one new word every 2ms. When these bits are changed, one calibration must be performed. In worst condition, the settle time of filter, reaching full-scale stepping input, is 4×(1/Output data rate). For example, the first notch is in 50Hz, and the settle time of filter is 80ms (max) for reaching full-scale input. If the first notch is in 500Hz, the settle time is 8ms (max). According to the synchronous stepping input, the settle time could be reduced to 3×(1/Output data rate). In other words, if stepping input occurs when FSYNC bit is high, it needs 3×(1/Output data rate) to settle after FSYNC bit returns to low.  -3dB frequency depends on the programmable first notch frequency,according to the equation below: Filter -3dB frequency=0.262×first notch frequency. |

|                  | 143.6 27.7 64.6 64.1 14.6 65.6 64.6 14.6 |     |             |                                  |  |  |  |  |  |  |

|------------------|------------------------------------------|-----|-------------|----------------------------------|--|--|--|--|--|--|

| CLK <sup>1</sup> | FS1                                      | FS0 | Output Rate | -3dB Cut-off Frequency of Filter |  |  |  |  |  |  |

| 0                | 0                                        | 0   | 20 Hz       | 5.24 Hz                          |  |  |  |  |  |  |

| 0                | 0                                        | 1   | 25 Hz       | 6.55 Hz                          |  |  |  |  |  |  |

| 0                | 1                                        | 0   | 100 Hz      | 26.2 Hz                          |  |  |  |  |  |  |

| 0                | 1                                        | 1   | 200 Hz      | 52.4 Hz                          |  |  |  |  |  |  |

| 1                | 0                                        | 0   | 50 Hz       | 13.1 Hz                          |  |  |  |  |  |  |

| 1                | 0                                        | 1   | 60 Hz       | 15.7 Hz                          |  |  |  |  |  |  |

| 1                | 1                                        | 0   | 250 Hz      | 65.5 Hz                          |  |  |  |  |  |  |

| 1                | 1                                        | 1   | 500 Hz      | 131 Hz                           |  |  |  |  |  |  |

Table 17. Output Rate Selection

Note 1: Assuming that the clock frequency of MCLK IN is correct, the setting of CLKDIV bit is also appropriate.

#### **Data Register (RS2, RS1, RS0 = 0,1,1)**

Data register is a 16-bit read-only register, which contains the latest conversion results from the MS7705/7706. If communication register sets device to write to the register, must perform one write operation to make device return the state, ready to perform write operation to communication register. But the written 16-bit data would be ignored by the MS7705/7706.

#### Test Register (RS2, RS1, RS0 = 1,0,0); Power On / Reset Status: 00Hex

Test register is used to test device. It is suggested that user should not change the default value of any bit in the test register.

### Zero-Scale Calibration Register (RS2, RS1, RS0 = 1,1,0); Power On / Reset Status: 1f4000Hex

The MS7705/7706 contains several independent zero-scale registers, each of which is responsible for one input channel. They are all 24-bit read/write registers. 24-bit data must be written before it can be transferred to the zero-scale calibration register. Zero-scale register is used together with full-scale register and form one register pair. And each pair responds to one pair of channel, see Table 9.

When device is set to allow access to these registers via digital interface, device itself doesn't access register coefficient in order to make output data correct scale. Therefore, after accessing to calibration register (whether read or write operation), the first output data read from device may contain uncorrected data. In addition, during data calibration, calibration register can't perform write operation. This type of events could be avoided by following method: Before calibration register starts operation, FSYNC bit in the mode register would be set as high level. After task is finished, FSYNC bit is set as low level.

### Full-Scale Calibration Register (RS2, RS1, RS0 = 1,1,1); Power on / Reset Status: 5761ABHex

The MS7705/7706 contains several independent full-scale registers, each of which is responsible for one input channel. They are all 24-bit read/write registers. 24-bit data must be written before it can be transferred to the full-scale calibration register. Full-scale register is used together with zero-scale register and form one register pair. And each pair responds to one pair of channel, see Table 9.

When device is set to allow access to these registers via digital interface, device itself doesn't access register coefficient in order to make output data correct scale. Therefore, after accessing to calibration register (whether read or write operation), the first output data read from device may contain uncorrected data. In addition, during data calibration, calibration register can't perform write operation. This type of events could be avoided by following method: Before calibration register starts operation, FSYNC bit in the mode register would be set as high level. After task is finished, FSYNC bit is set as low level.

#### **Calibration Process**

Table 18 summarizes these calibration types, operation contents and operation time. There are two ways to judge whether the calibration is over. The first method is to monitor DRDY. If DRDY returns to low level, it indicates that the calibration process has finished and that there is a new valid data in the data register. The second method is to monitor MD1 and MD0 bits in the setting register. If MD1 and MD0 return to "0" (after calibration, MD1 and MD0 return to "0"), it indicates that the calibration process has finished. This method can not prompt whether there is a new conversion result in the data register, but it's earlier than the first judgment method in time, that is, that is, it can quickly know whether the calibration has finished. The duration time when Mode bits (i.e. MD1, MD0) return to "0" is shown in Table 18. The process of DRDY returning to low level includes a normal conversion time and a delay time tp with correct scale for the first conversion result. tp shall not exceed 2000 × tCLKIN. The time required for these two methods is shown in the table below.

Calibration Type MD1,MD0 **DRDY Setting Time** Calibration Sequence **Setting Time** Zero-scale Calibration @ **Self Calibration** 9 ×1/Output rate+tP 0,1 Selected Gain + Full-scale 6 ×1/Output Rate Calibration @ Selected Gain Zero-scale Zero-scale Calibration 1,0 3 ×1/Output Rate 4 ×1/Output rate+tP Calibration @ Selected Gain Full-Scale **Full-scale Calibration** 3 ×1/Output Rate 1×1/Output rate+tP 1,1, Calibration @ Selected Gain

Table 18. Calibration Process

### **Analog Input Range**

In non-buffered mode, the common-mode input range is from GND to VDD. The absolute value of analog input voltage is between GND-30mV and VDD+30mV. In non-buffer mode, the analog input connects directly to a 7pF sampling capacitor, C<sub>SAMP</sub>. As a result, the analog input connects a dynamic load that is converted at the input sampling rate. The typical value of the effective on-off resistance (R<sub>SW</sub>) of the switch is 7K. Table 19 lists the allowable external resistance/capacitance values in non-buffer mode.

Table 19. External Resistance and Capacitance Values without 16-Bit Gain Error (Non-buffer Mode)

|      |       | External Capacitance(pF) |         |        |        |        |        |  |  |

|------|-------|--------------------------|---------|--------|--------|--------|--------|--|--|

| Gain | Gain  | 10                       | 50      | 100    | 500    | 1000   | 5000   |  |  |

|      | 1     | 152kΩ                    | 53.9kΩ  | 31.4kΩ | 8.4kΩ  | 4.76kΩ | 1.36kΩ |  |  |

|      | 2     | 75.1kΩ                   | 26.6kΩ  | 15.4kΩ | 4.14kΩ | 2.36kΩ | 670Ω   |  |  |

|      | 4     | 34.2kΩ                   | 12.77kΩ | 7.3kΩ  | 1.95kΩ | 1.15kΩ | 320Ω   |  |  |

|      | 8~128 | 16.7kΩ                   | 5.95kΩ  | 3.46kΩ | 924Ω   | 526Ω   | 150Ω   |  |  |

#### **Sampling Rate**