# BL6552 Professional chip for three phase power monitoring and analysis Data Sheet

V1.12

# Table of contents

| 1、     |       | Produ     | uct description                                             | 6     |

|--------|-------|-----------|-------------------------------------------------------------|-------|

| 2、     |       | Basic     | c Features                                                  | 7     |

| 2      | 2. 1  | M         | Main feature                                                | 7     |

| 2      | 2. 2  | 5         | System Block Diagram                                        | 8     |

| 2      | 2. 3  | F         | Pin arrangement                                             | 9     |

| 2      | 2. 4  | F         | Performance indicators                                      | 10    |

|        |       | 2. 4. 1   | 1 Electrical parameter performance index                    | 10    |

|        |       | 2. 4. 2   | 2 Limit range                                               | 11    |

| 3、     |       | Worki     | ing principle                                               | 13    |

| 3      | 3. 1  | F         | Principle of current and voltage waveform generation        | 13    |

|        |       | 3. 1. 1   | 1 Active phase compensation                                 | 14    |

|        |       | 3. 1. 2   | 2 Channel offset correction                                 | 15    |

|        |       | 3. 1. 3   | 3 Channel gain correction                                   | 16    |

|        |       | 3. 1. 4   | 4 Current and voltage waveform output                       | 17    |

| 3      | 3. 2  | F         | Principle of active power calculation                       |       |

|        |       | 3. 2. 1   | 1 Active power output                                       |       |

|        |       | 3. 2. 2   | 2 Active power calibration                                  | 19    |

|        |       | 3. 2. 3   | 3 Active power anti-creeping                                | 20    |

|        |       | 3. 2. 4   | 4 Active power small signal compensation                    | 21    |

|        |       | 3. 2. 5   | 5 Active power selection                                    | 21    |

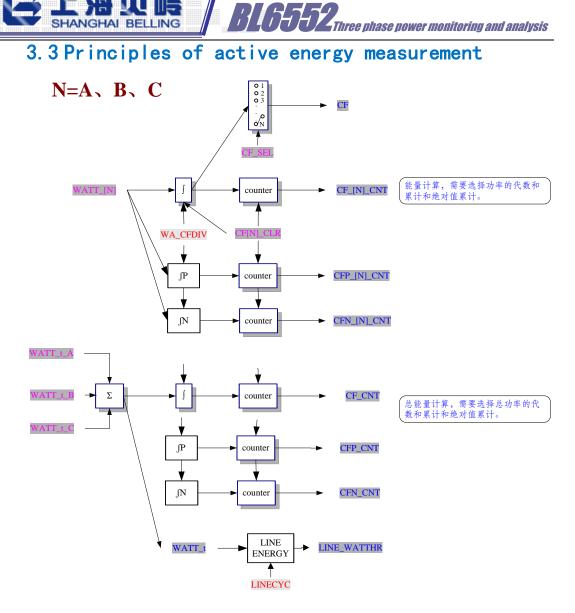

| 3      | 3. 3  | F         | Principles of active energy measurement                     | 22    |

|        |       | 3. 3. 1   | 1 Active energy output                                      | 23    |

|        |       | 3. 3. 2   | 2 Active energy pulse output selection                      | 23    |

|        |       | 3. 3. 3   | 3 Active energy pulse output ratio                          | 24    |

| 3      | 3. 4  | C         | Calculation principle of the effective value of current and |       |

| ١      | /0 1  | tage 2    | 25                                                          |       |

|        |       | 3. 4. 1   | 1 Effective value output                                    | 25    |

|        |       | 3. 4. 2   | 2 Setting of effective value input signal                   |       |

|        |       | 3. 4. 3   | 3 Valid value refresh rate setting                          |       |

|        |       | 3. 4. 4   | 4 Current and voltage RMS calibration                       |       |

|        |       | 3. 4. 5   | 5 Effective value of anti-creeping                          | 27    |

| 3      | 3. 5  | F         | Fast RMS detection principle                                |       |

|        |       | 3. 5. 1   | 1 Fast RMS output                                           |       |

|        |       | 3. 5. 2   | 2 Fast RMS input selection                                  | 29    |

|        |       | 3. 5. 3   | 3 Fast RMS cumulative time                                  | 29    |

|        |       | 3. 5. 4   | 4 Grid frequency selection                                  |       |

| Shangl | hai E | Belling ( | Co., Ltd. 2/93                                              | V1.12 |

**BIG552**Three phase power monitoring and analysis

| Ľ  | BIG552 Three phase power monitoring an                                                 | d analysis |

|----|----------------------------------------------------------------------------------------|------------|

| _  | 3.6 Reactive power calculation                                                         |            |

|    | 3.6.1 Reactive phase compensation                                                      |            |

|    | 3.6.2 Reactive power output                                                            |            |

|    | 3.6.3 Reactive power calibration                                                       |            |

|    | 3.6.4 Anti-creeping of reactive power                                                  |            |

|    | 3.6.5 Reactive power small signal compensation                                         |            |

|    | 3.6.6 Reactive energy output                                                           | 34         |

|    | 3.7 Calculation of Apparent and Power Factor                                           | 35         |

|    | 3.7.1 Apparent power and energy output                                                 |            |

|    | 3.7.2 Apparent power calibration                                                       | 37         |

|    | 3.7.3 Power factor                                                                     |            |

|    | 3.8 Calculation of the sum of three-phase currents                                     |            |

|    | 3.8.1 The output of the current sum                                                    |            |

|    | 3.8.2 Adjustment of current sum                                                        |            |

|    | 3.8.3 Comparison of current sum                                                        |            |

|    | 3.9 Small signal compensation                                                          |            |

|    | 3.10 Electrical parameter measurement                                                  | 40         |

|    | 3.10.1 Line cycle measurement                                                          | 40         |

|    | 3.10.2 Line frequency measurement                                                      | 41         |

|    | 3.10.3 Phase angle calculation                                                         | 41         |

|    | 3.10.4 Power sign bit                                                                  |            |

|    | 3.11 Fault detection                                                                   |            |

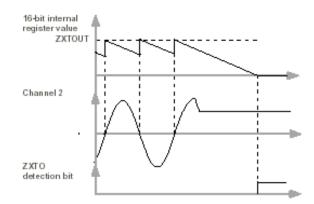

|    | 3.11.1 Zero crossing detection                                                         |            |

|    | 3.11.2 Peak Detection                                                                  |            |

|    | 3.11.3 SAG Detection                                                                   |            |

|    | 3.11.4 Zero-crossing Timeout                                                           |            |

|    | 3.11.5 Zero-crossing Detection                                                         |            |

|    | 3.11.6 Power supply Detection                                                          |            |

| 4、 | Internal registers                                                                     |            |

|    | 4.1 Electrical parameter register (external read)                                      |            |

|    | 4.2 Calibration register 1                                                             |            |

|    | 4.3 Calibration register 2                                                             |            |

|    | 4.4 Detailed description of calibration register                                       |            |

|    | 4.4.1 Channel PGA gain adjustment register<br>4.4.2 Phase correction related registers |            |

|    | 4.4.2 Phase correction related registers                                               |            |

|    | 4.4.3 RMS offset correction register                                                   |            |

|    |                                                                                        |            |

| <b>BIG552</b> Three phase power monitoring and             | analysis |

|------------------------------------------------------------|----------|

| 4.4.4 Power small signal compensation register             |          |

| 4.4.5 Anti-creep threshold register                        |          |

| 4.4.6 Fast effective value related setting register        | 65       |

| 4.4.7 Fault detection related registers                    | 65       |

| 4.4.8 ADC enable control                                   | 65       |

| 4.4.9 Mode register 1                                      | 65       |

| 4.4.10 Mode register 2                                     | 66       |

| 4.4.11 Mode register 3                                     | 66       |

| 4.4.12 Interrupt status register                           | 67       |

| 4.4.13 Interrupt mask register                             | 69       |

| 4.4.14 Clear the setting register after energy read        | 70       |

| 4.4.15 User write protection setting register              | 70       |

| 4.4.16 Soft reset command                                  | 70       |

| 4.4.17 Channel gain adjustment register                    | 71       |

| 4.4.18 Channel offset adjustment register                  | 71       |

| 4.4.19 Power gain adjustment register                      | 72       |

| 4.4.20 Power offset adjustment register                    | 73       |

| 4.4.21 CF scaling register                                 | 74       |

| 4.4.22 AT1~3 logic output pin configuration register       | 75       |

| 4.5 Detailed description of electrical parameter registers | 77       |

| 4.5.1 Wave register                                        | 77       |

| 4.5.2 RMS register                                         |          |

| 4.5.3 Fast RMS register                                    | 78       |

| 4.5.4 Active power register                                | 78       |

| 4.5.5 Reactive power register                              | 79       |

| 4.5.6 Apparent power register                              | 80       |

| 4.5.7 Energy pulse count register                          | 81       |

| 4.5.8 Waveform angle register                              |          |

| 4.5.9 Power factor register                                |          |

| 4.5.10 Line voltage frequency register                     |          |

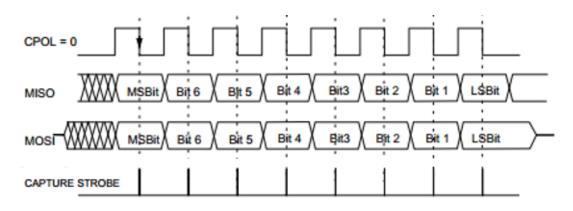

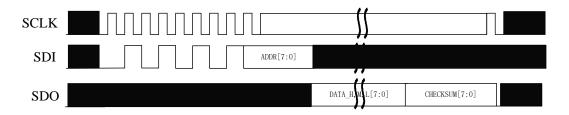

| 5. Communication Interface                                 |          |

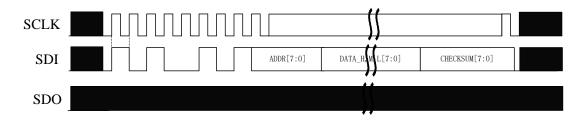

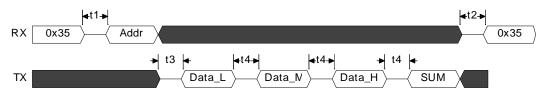

| 5. 1 SPI                                                   |          |

| 5.1.1 Overview                                             |          |

| 5.1.2 Operating mode                                       |          |

| 5.1.3 Frame structure                                      |          |

| 5.1.4 Read operation timing                                |          |

| 5.1.5 Write operation timing                               |          |

#### B6552 Three phase power monitoring and analysis BELLING 6、 6.1 6.2 6.3

# SHANGHAI BELLING **BLG5552** Three phase power monitoring and analysis Product description

1、

BL6552 is a 7-channel three-phase power monitoring and analysis chip, which is suitable for three-phase intelligent circuit breaker, three-phase guide rail meter, electrical measuring instrument, power supply monitoring of high-power equipment and other applications, with high cost performance.

BL6552 integrates seven high-precision Sigma-Delta ADCs, reference voltage circuits, temperature sensors and other analog circuit modules, as well as digital signal processing circuits for processing power, effective value, energy, temperature and other electrical parameters. It can be used to measure the total (fundamental and harmonic) active power and energy, reactive power and energy, apparent power and energy of three-phase split and combined phase; and fundamental active power and energy, reactive power and energy; And each phase current, voltage effective value, power factor and other parameters; with current loss monitoring, current and voltage peak detection, zero-crossing detection and other power quality management; can give real-time waveforms.

BL6552 integrates SPI and UART interfaces to facilitate the transfer of metering parameters and calibration parameters with an external MCU.

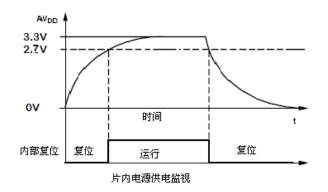

BL6552 internally uses data flow calculation method to process various signals, and it has good reliability in the case of external interference. The internal power supply voltage monitoring circuit can ensure normal operation during power-up and power-off.

# 2. Basic Features 2.1 Main feature

- ✓ High-precision, 8000:1 input dynamic range of active energy measurement nonlinear error <0.1%</p>

- ✓ High stability, non-linear error of reactive energy measurement within the input dynamic range of 8000:1 <0.1%</p>

**BLG5552**Three phase power monitoring and analysis

- ✓ Provide neutral current measurement

- ✓ Provide split-phase and total (fundamental and harmonic) active, reactive, and apparent power (24bit, supporting two calculation methods); and fundamental active and reactive power (24bit)

- ✓ Provide the effective value of split-phase voltage and current (24bit), and the relative error within the detection range of 3000:1 is less than 0.1%

- Provide waveform sampling data of split-phase voltage, current and neutral current (24bit)

- Provide total (fundamental and harmonic) active, reactive, and apparent energy (24bit)

- ✓ Provide total (fundamental and harmonic) active and reactive line cycle energy

- ✓ Provide total (fundamental and harmonic) positive and negative active energy

- ✓ Provide the combined and four-quadrant reactive energy

- ✓ Provides 300 real-time waveforms per week

- ✓ Provide split-phase and combined-phase power factor

- ✓ With fast effective value output

- ✓ Provide voltage and current phase angle measurement

- $\checkmark$  Fast pulse output with active energy and reactive energy

- $\checkmark$  With voltage loss and phase failure detection function

- $\checkmark$  With current loss detection function

- $\checkmark$  With current and voltage peak detection and zero-crossing detection functions

- $\checkmark$  With voltage line frequency detection

- ✓ Programmable anti-creep threshold setting

- ✓ Programmable adjustment of pulse output frequency

- Programmable active power, reactive power, apparent power error and gain adjustment

- ✓ Programmable input active phase compensation

- ✓ With UART/SPI communication interface for easy data transmission

- ✓ Built-in reference voltage source

- ✓ Single power supply 3.3V

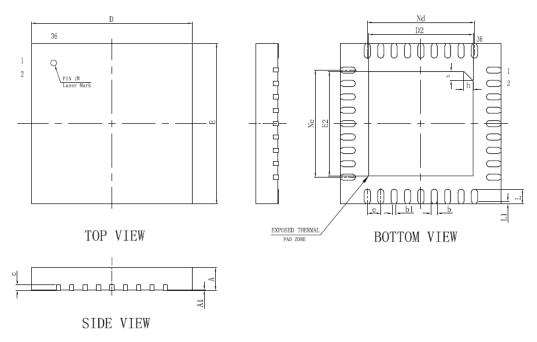

- ✓ QFN36 PACKAGE

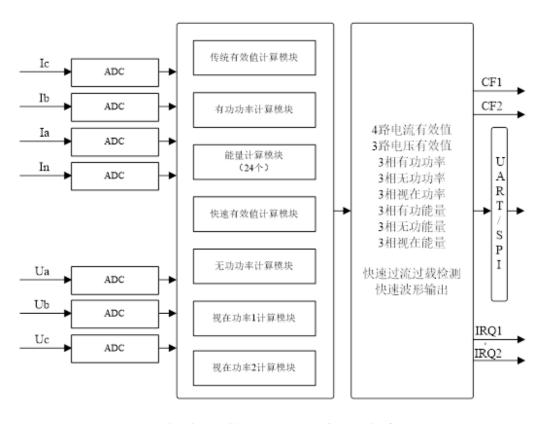

# 2.2 System Block Diagram

### 三相电能监测及分析专用芯片

It is mainly divided into analog signal processing and digital signal processing. The analog part mainly includes 7-channel high-precision Sigma-Delta ADC and related analog modules, and the digital part is a digital signal processor and related modules.

SHANGHAL BELLING BLG552Three phase power monitoring and analysis

# 2.3 Pin arrangement

QFN36 PACKAGE

| Seria<br>1<br>num<br>ber | Nam<br>e   | Input output    | Description                                                                                                          |  |  |

|--------------------------|------------|-----------------|----------------------------------------------------------------------------------------------------------------------|--|--|

| 1                        | INP        | input           | Positive terminal input of neutral current channel                                                                   |  |  |

| 2                        | VRE<br>F   | input output    | The reference voltage output pin is connected with a 0.1uF filter capacitor.                                         |  |  |

| 3                        | VAN        | input           | A phase voltage channel negative terminal input, the maximum differential voltage of each pair of pins is $\pm 0.7V$ |  |  |

| 4                        | VAP        | input           | A phase voltage channel positive terminal input                                                                      |  |  |

| 5                        | VBN        | input           | B-phase voltage channel negative terminal input, the maximum differential voltage of each pair of pins is $\pm 0.7V$ |  |  |

| 6                        | VBP        | input           | B-phase voltage channel positive terminal input                                                                      |  |  |

| 7                        | VCN        | input           | C-phase voltage channel negative terminal input, the maximum differential voltage of each pair of pins is $\pm 0.7V$ |  |  |

| 8                        | VCP        | input           | C-phase voltage channel positive terminal input                                                                      |  |  |

| 9                        | NRS<br>T   | input           | Reset, active low                                                                                                    |  |  |

| 10                       | AGN<br>D   | Power<br>ground | Analog ground                                                                                                        |  |  |

| 11                       | DGN<br>D   | Power<br>ground | Digital ground                                                                                                       |  |  |

| 12                       | CS         | input           | SPI chip selection/UART rate selection                                                                               |  |  |

| 13                       | SDO        | output          | SPI/UART transmit data pin                                                                                           |  |  |

| 14                       | SDI        | input           | SPI/UART receive data pin                                                                                            |  |  |

| 15                       | SCL<br>K   | input           | SPI clock input/UART rate selection                                                                                  |  |  |

| 16                       | IRQ1       | output          | Interrupt status logic output 1                                                                                      |  |  |

| 17                       | IRQ2       | output          | Interrupt status logic output 2                                                                                      |  |  |

| 18                       | CLK<br>OUT | output          | Crystal oscillator pin                                                                                               |  |  |

| 19                       | CLK<br>IN  | input           | Crystal oscillator pin, external crystal oscillator frequency<br>8MHz                                                |  |  |

| 20                       | VPP        | power<br>supply | Reserved, can be left floating                                                                                       |  |  |

| 21                       | CF1        | output          | Calibration pulse 1 (active power)                                                                                   |  |  |

| 22                       | CF2        | output          | Calibration pulse 2 (reactive power)                                                                                 |  |  |

| 23                       | AT1        | output          | Logic output pin, configurable output indication 1                                                                   |  |  |

| 24                       | AT2        | output          | Logic output pin, configurable output indication 2                                                                   |  |  |

| 25                       | AT3        | output          | Logic output pin, configurable output indication 3                                                                   |  |  |

Shanghai Belling Co., Ltd.

|    |       | an K         |                                                                 |      |         |                                                         |

|----|-------|--------------|-----------------------------------------------------------------|------|---------|---------------------------------------------------------|

| Ŀ  | SHAN  | SHAI BELLING | <b>BL6552</b> Three phase power monitoring and analysis         |      |         |                                                         |

| 26 | DVD   |              |                                                                 |      |         |                                                         |

| 26 | D18   | output       | Digital module voltage 1.8V, external 0.1uF filter capacitor    |      |         |                                                         |

| 27 | SEL   | input        | Default 0, select Uart; 1, select SPI                           |      |         |                                                         |

| 20 | DVD   | power        | Deriver sympley 2.2M                                            |      |         |                                                         |

| 28 | D     | supply       | Power supply 3.3V                                               |      |         |                                                         |

| 20 | AVD   | power        | Deriver even h. 2.2M                                            |      |         |                                                         |

| 29 | D     | supply       | Power supply 3.3V                                               |      |         |                                                         |

| 30 | ICN   | input        | C-phase current channel negative terminal input, the maximum    |      |         |                                                         |

| 30 | ICN   | input        | differential voltage of each pair of pins is $\pm 0.7V$         |      |         |                                                         |

| 31 | ICP   | input        | C-phase current channel positive terminal input                 |      |         |                                                         |

| 32 | IBN   | input        | B-phase current channel negative terminal input, the maximum    |      |         |                                                         |

| 32 | IDIN  | IDIN         | IBN                                                             | IDIN | N input | differential voltage of each pair of pins is $\pm 0.7V$ |

| 33 | IBP   | input        | B-phase current channel positive terminal input                 |      |         |                                                         |

| 34 | IAN   | input        | A phase current channel negative terminal input, the maximum    |      |         |                                                         |

| 54 | IAN   | input        | differential voltage of each pair of pins is $\pm 0.7$ V        |      |         |                                                         |

| 35 | IAP   | input        | A phase current channel positive terminal input                 |      |         |                                                         |

| 36 | INN   | input        | Negative terminal input of the neutral current channel, the     |      |         |                                                         |

| 50 | 11111 | input        | maximum differential voltage of each pair of pins is $\pm 0.7V$ |      |         |                                                         |

Remarks: The maximum differential voltage of the analog input pins refers to the channel 1 times gain, if other gains are set, the maximum differential voltage of the channel will be reduced accordingly;

# 2.4 Performance indicators

### 2.4.1 Electrical parameter performance index

| Parameter            | Symbol               | Test Condition            | Measure | Min | Тур  | Max | Unit |

|----------------------|----------------------|---------------------------|---------|-----|------|-----|------|

|                      |                      |                           | Pin     |     |      |     |      |

| Active power         | WATTERR              | 8000:1 input DR           |         |     | 0.1  |     | %    |

| measurement error    |                      |                           |         |     |      |     |      |

| Reactive power       | VAR <sub>ERR</sub>   | 8000:1 input DR           |         |     | 0.1  |     | %    |

| measurement error    |                      |                           |         |     |      |     |      |

| Phase angle between  |                      |                           |         |     |      |     |      |

| channels causes      |                      |                           |         |     |      |     |      |

| measurement errors   | PF08C <sub>ERR</sub> | Phase lead 37°            |         |     | 0.1  |     | %    |

| (PF=0.8 capacitive)  | PF05L <sub>err</sub> | Phase lag 60°             |         |     | 0.1  |     | %    |

| (PF=0.5 inductive)   |                      |                           |         |     |      |     |      |

| AC power supply      | AC <sub>PSRR</sub>   | Current channel current   |         |     | 0.01 |     | %    |

| suppression          |                      | input pin IP\IN@100mV,    |         |     |      |     |      |

| (variation of output | DC <sub>PSRR</sub>   | voltage channel input pin |         |     | 0.1  |     | %    |

| frequency amplitude) |                      | VP\VN=100mV               |         |     |      |     |      |

| DC power supply      |                      |                           |         |     |      |     |      |

| suppression          |                      |                           |         |     |      |     |      |

| (variation of output  |                     |                        |     |       |     |        |

|-----------------------|---------------------|------------------------|-----|-------|-----|--------|

| frequency amplitude)  |                     |                        |     |       |     |        |

| Voltage RMS           | VRMS <sub>ERR</sub> | 3000:1 input DR        |     | 0.1   |     | %      |

| measurement           |                     |                        |     |       |     |        |

| accuracy, relative    |                     |                        |     |       |     |        |

| error                 |                     |                        |     |       |     |        |

| Current RMS           | IRMS <sub>ERR</sub> | 3000:1 input DR        |     | 0.1   |     | %      |

| measurement           |                     |                        |     |       |     |        |

| accuracy, relative    |                     |                        |     |       |     |        |

| error                 |                     |                        |     |       |     |        |

| Analog input input    |                     | PGA=1                  |     |       |     |        |

| level (peak value)    |                     | Differential input     |     |       | 700 | mV     |

| input resistance      |                     |                        | 370 |       |     | kΩ     |

| Signal bandwidth (-   |                     |                        |     | 14    |     | kHz    |

| 3dB) Gain error       |                     | External 1.2 reference |     | 0.5   |     | %      |

| Phase gain matching   |                     | voltage                |     | 0.3   |     | %      |

| error                 |                     | External 1.2 reference |     |       |     |        |

|                       |                     | voltage                |     |       |     |        |

| Internal voltage      | Vref                |                        |     | 1.097 |     | V      |

| reference             | TempCoef            |                        |     | 20    |     | ppm/°C |

| temperature           |                     |                        |     |       |     |        |

| coefficient           |                     |                        |     |       |     |        |

| Logic input pin Input |                     | NRST, SDI, SCLK,       |     |       |     |        |

| high level Input low  |                     | /CS                    | 2.6 |       |     | V      |

| level                 |                     | DVDD=3.3V±2.5%         |     |       | 0.8 | V      |

|                       |                     | DVDD=3.3V±2.5%         |     |       |     |        |

| Logic output pin      |                     | SDO、CF1、CF2、           |     |       |     |        |

| Output high level     |                     | AT1, AT2, AT3          |     |       |     |        |

| Output low level      |                     | DVDD=3.3V±2.5%         | 2.6 |       |     | V      |

|                       |                     | DVDD=3.3V±2.5%         |     |       | 1   | V      |

| power supply          |                     |                        |     |       |     |        |

| AVDD、DVDD             | V <sub>AVDD</sub>   |                        | 3   | 3.3   | 3.6 | V      |

| DVDD18                | V <sub>DVDD18</sub> |                        | 1.6 | 1.8   | 2   | V      |

| AVDD                  | I <sub>AVDD</sub>   | AVDD=3.3               |     | 6     | 9   | mA     |

| DVDD                  | I <sub>DVDD</sub>   | DVDD=3.3               |     | 6     | 9   | mA     |

## 2.4.2 Limit range

(T = 25 °C)

| Project                        | Symbol    | Extremum    | Unit |

|--------------------------------|-----------|-------------|------|

| Power supply voltage<br>VDD    | AVDD、DVDD | -0.3 ~ +4   | V    |

| Power supply voltage<br>DVDD18 | DVDD18    | -0.3 ~ +2.5 | V    |

Shanghai Belling Co., Ltd.

| BL6552 Three phase power monitoring and | analysis |

|-----------------------------------------|----------|

|-----------------------------------------|----------|

| Analog input voltage<br>(relative to GND)   | ICN、ICP、IBN、IBP、<br>IAN、IAP、INN、INP、<br>VCN、VCP、VBN、VBP、<br>VAN、VAP | -1 ~ +AVDD      | V  |

|---------------------------------------------|---------------------------------------------------------------------|-----------------|----|

| Analog output voltage<br>(relative to GND)  | VREF                                                                | -0.3 ~ +AVDD    | V  |

| Digital input voltage<br>(relative to GND)  | SEL、NRST、SDI、SCLK、<br>/CS、SEL                                       | -0.3 ~ AVDD+0.3 | V  |

| Digital output voltage<br>(relative to GND) | CF1、CF2、SDO                                                         | -0.3 ~ AVDD+0.3 | V  |

| Operating temperature                       | Topr                                                                | -40 ~ +85       | °C |

| Storage temperature                         | Tstr                                                                | -55 ~ +150      | °C |

| Power consumption<br>(QFN36)                | Р                                                                   | 200             | mW |

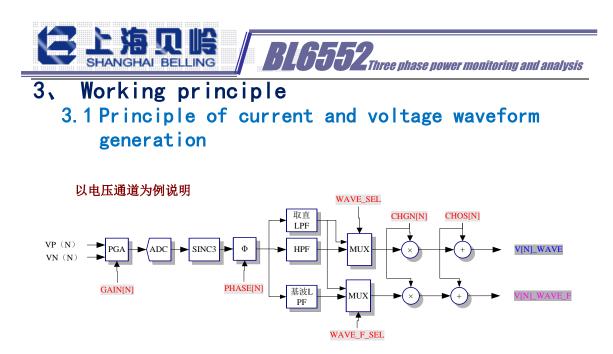

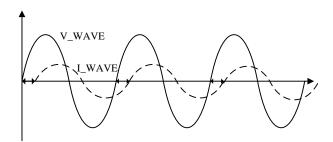

There are 7 high-precision ADCs in total, using double-ended differential signal input: channel N input signal VP[N] and VN[N]. 7 waveform outputs, including 4 currents and 3 voltages. In each channel (the current and voltage are the same), the input signal passes the analog module amplifier (PGA) and high-precision analog-to-digital conversion (ADC) to get 1bit PDM to the digital module. The digital module undergoes phase calibration and down-sampling filter (SINC3), optional high-pass filter (HPF) or fundamental wave low-pass filter, through gain and offset correction modules, to obtain the required current waveform data and voltage waveform data (I[N]\_WAVE, V[N] WAVE ).

7-channel PGA gain is adjustable (0000=1 times; 0001=2 times; 0010=8 times; 0011=16 times), see GAIN register for adjustment

|    | Address | Name  | Bit width | Defaults | Description                                   |

|----|---------|-------|-----------|----------|-----------------------------------------------|

| ſ  |         |       |           |          | Channel PGA gain adjustment register:         |

| 60 | 60      |       | 24        | 0x000000 | [11:8]: C-phase current [15:12]: B-phase      |

|    | 00      | GAIN1 | 24        |          | current [19:16]: Phase A current [23:20]:     |

|    |         |       |           |          | Neutral line current                          |

|    |         |       |           |          | Channel PGA gain adjustment register: [11:8]: |

|    | 61      | GAIN2 | 20        | 0x00000  | Phase A voltage [15:12]: Phase B voltage      |

|    |         |       |           |          | [19:16]: Phase C voltage                      |

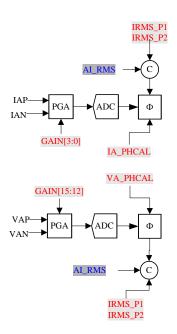

### 3.1.1 Active phase compensation

The chip provides a method for digital calibration of small phase errors. It can introduce a small time delay or lead into the signal processing circuit to compensate for small phase errors. Since this compensation needs to be timely, this method is only suitable for small phase errors in the range of  $<0.574^{\circ}$ .

**BL6552**Three phase power monitoring and analysis

Since the transformer at the analog input terminal may have inconsistent angle differences when input signals of different amplitudes, increase the angle differential section compensation setting and allow three-section angle differential compensation.

Current channel angle differential segment definition register:

| Address | Name    | Bit width | Defaults | Description                                     |

|---------|---------|-----------|----------|-------------------------------------------------|

|         |         |           |          | The angle difference segment point defines      |

| 62      | IRMS_P1 | 24        | 0x010000 | P1, which satisfies                             |

|         |         |           |          | IRMSmin <p1<p2<irmsmax< td=""></p1<p2<irmsmax<> |

|         |         |           |          | The angle difference segment point defines      |

| 63      | IRMS_P2 | 24        | 0x200000 | P2, which satisfies                             |

|         |         |           |          | IRMSmin <p1<p2<irmsmax< td=""></p1<p2<irmsmax<> |

The phase calibration register is a binary 24-bit register, and the data format of each register is as follows:

|         | SHANGHAI BELLING <b>BLOOD</b> Three phase power monitoring and analy |           |          |                                                                                                                           |  |  |

|---------|----------------------------------------------------------------------|-----------|----------|---------------------------------------------------------------------------------------------------------------------------|--|--|

| Address | Name                                                                 | Bit width | Defaults | Description                                                                                                               |  |  |

| 64      | IA_PHCAL                                                             | 24        | 0x000000 | A phase current channel angle difference correction register,                                                             |  |  |

| 65      | IB_PHCAL                                                             | 24        | 0x000000 | B-phase current channel angle difference correction register (same as above)                                              |  |  |

| 66      | IC_PHCAL                                                             | 24        | 0x000000 | C-phase current channel angle difference<br>correction register (same as above)                                           |  |  |

| 67      | VA_PHCAL                                                             | 24        | 0x000000 | A phase voltage channel angle difference correction register,                                                             |  |  |

| 68      | VB_PHCAL                                                             | 24        | 0x000000 | B-phase voltage channel angle difference correction register (same as above)                                              |  |  |

| 69      | VC_PHCAL                                                             | 24        | 0x000000 | C-phase voltage channel angle difference correction register (same as above)                                              |  |  |

| 90      | IN_PHCAL                                                             | 24        | 0x000000 | The angle difference correction register of<br>the IN phase current channel has the same<br>adjustment accuracy as above. |  |  |

### 3.1.2 Channel offset correction

合上海见岭 / риссер

Contains 7 16-bit channel offset calibration registers XX\_CHOS, the default value is 0x0000.

These registers can be used for digital calibration or error pre-calibration before leaving the factory.

They use the data in the form of 2's complement to eliminate the deviation caused by the analog-to-digital conversion of the current channel and the voltage channel respectively. The deviation here may be due to the input and offset produced by the analog-to-digital conversion circuit itself. Deviation correction can make the waveform offset to 0 under no load.

| Address | Name           | Bit width | Defaults             | Description                         |

|---------|----------------|-----------|----------------------|-------------------------------------|

| AC      | IC CHOS        | 16        | 0x0000               | Current C channel offset adjustment |

|         |                | 010000    | register, complement |                                     |

| AD      | IP CHOS        | 16        | 0x0000               | Current B channel offset adjustment |

| AD      | IB_CHOS        | 16        | 0x0000               | register, complement                |

| AE      |                | 16        | 0x0000               | Current A channel offset adjustment |

| AE      | IA_CHOS        | 16        |                      | register, complement                |

| 4.5     | F IN_CHOS 16 ( | 1.5       | 0.0000               | Current N channel offset adjustment |

| AF      |                | 0x0000    | register, complement |                                     |

| B2 | VA_CHOS | 16 | 0x0000 | Voltage A channel offset adjustment register, complement    |

|----|---------|----|--------|-------------------------------------------------------------|

| B3 | VB_CHOS | 16 | 0x0000 | Voltage B channel offset adjustment<br>register, complement |

| B4 | VC_CHOS | 16 | 0x0000 | Voltage C channel offset adjustment register, complement    |

These registers are used for channel deviation calibration

Correction formula:

#### $XX_WAVE[N] = XX_WAVE0[N] + XX_CHOS$

Where XX\_WAVE0[N] is the measured value of the corresponding channel, XX\_CHOS is the calibration value, and XX\_WAVE is the output value after calibration. 3. 1. 3 Channel gain correction

Contains 7 16-bit channel gain calibration registers XX\_CHGN, the default value is 0x0000.

These registers can be used for digital calibration or error pre-calibration before leaving the factory.

They adjust the gain error caused by the analog-to-digital conversion of the current channel and the voltage channel with data in the form of 2's complement. The error here may be caused by the input and the analog-to-digital conversion circuit itself. Gain correction can be adjusted within  $\pm 50\%$ .

| Address | Name    | Bit width | Defaults | Description                       |

|---------|---------|-----------|----------|-----------------------------------|

| A1      | IC CHGN | 16        | 0x0000   | Current C channel gain adjustment |

|         |         |           |          | register, complement              |

| A2      | IB_CHGN | 16        | 0x0000   | Current B channel gain adjustment |

| 112     | ID_CHON | 10        | 0,0000   | register, complement              |

| A3      | IA_CHGN | 16        | 0x0000   | Current A channel gain adjustment |

| AS      | IA_CHON | 10        | 0x0000   | register, complement              |

| A4      | IN CHCN | 10        | 00000    | Current N channel gain adjustment |

| A4      | IN_CHGN | 16        | 0x0000   | register, complement              |

| A7      | VA CHCN | 16        | 0x0000   | Voltage A channel gain adjustment |

| Α/      | VA_CHGN | 16        |          | register, complement              |

| A Q     | VD CUCN | 16        | 0x0000   | Voltage B channel gain adjustment |

| A8      | VB_CHGN | 16        |          | register, complement              |

| 10      | NG CHON | 16        | 0.0000   | Voltage C channel gain adjustment |

| A9      | VC_CHGN | 16        | 0x0000   | register, complement              |

These registers are used for channel gain calibration

Correction formula:

$$XX_WAVE = XX_WAVE0[N] * (1 + \frac{XX_CHGN}{2^{16}})$$

**B6552**Three phase power monitoring and analysis

Where XX\_WAVE0 is the measurement value of the corresponding channel, XX\_CHGN is the gain calibration value, and XX\_WAVE is the calibration output value.

### 3.1.4 Current and voltage waveform output

The current load current and voltage waveform data can be collected, the sampling current and voltage are updated at a rate of 15.6ksps, and about 312 points can be sampled per cycle. Each sampled data is a 24-bit signed number, and is stored in the waveform register (I[N]\_WAVE, V[N]\_WAVE). The maximum SPI rate is 1.5Mbps, and the waveform values of multiple channels can be read continuously.

The channels can be selected through HPF, fundamental wave LPF, and finally 7-channel waveforms are obtained.

| Address | Name    | Bit width | Defaults | Description                       |

|---------|---------|-----------|----------|-----------------------------------|

| 2       | IC_WAVE | 24        | 0x000000 | C-phase current waveform register |

| 3       | IB_WAVE | 24        | 0x000000 | B-phase current waveform register |

| 4       | IA_WAVE | 24        | 0x000000 | A-phase current waveform register |

| 5       | IN_WAVE | 24        | 0x000000 | Neutral current waveform register |

| 8       | VA_WAVE | 24        | 0x000000 | A-phase voltage waveform register |

| 9       | VB_WAVE | 24        | 0x000000 | B-phase voltage waveform register |

| А       | VC_WAVE | 24        | 0x000000 | C-phase voltage waveform register |

The waveform is divided into full wave and fundamental wave. The HPF is the AC measurement mode, and the full-wave waveform is output. Through fundamental

wave LPF as fundamental wave measurement mode, output fundamental wave waveform.

The waveform output selection is fixed, and it is set by the user mode register

### MODE1[23].

| 0x96 | MODE1        | Operating mode register |                                                                                                                                                                                       |  |  |

|------|--------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| No.  | name         | default value           | description                                                                                                                                                                           |  |  |

| [23] | WAVE_REG_SEL | 1'b0                    | Current WAVE waveform register output<br>selection, default 0 to select the waveform of<br>the normal current channel, 1 to select the<br>waveform output of the fast current channel |  |  |

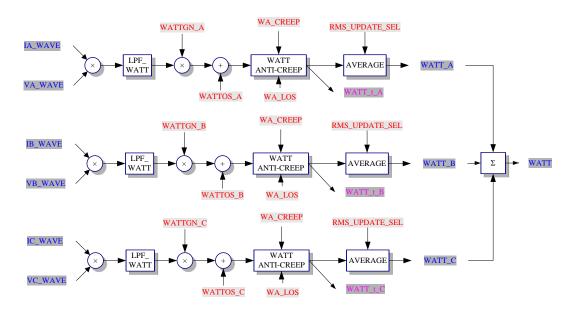

### 3.2 Principle of active power calculation

The three-phase current and voltage waveforms are respectively digitally multiplied, and then passed through the low-pass filter, gain and deviation calibration, anti-creeping judgment and averaging in order to obtain the split-phase power signal, which is added to obtain the total active power.

### 3.2.1 Active power output

Corresponding to the three-phase currents are multiplied by the three-phase voltages to obtain the three-phase power signal, which is added to obtain the total power.

|                            | Address | Name | Bit width | Defaults | Description |       |

|----------------------------|---------|------|-----------|----------|-------------|-------|

| Shanghai Belling Co., Ltd. |         |      |           | 18/93    |             | V1.12 |

Shanghai Belling Co., Ltd.

|   | WATT A | 0x000000 | A-phase active power register (full wave    |

|---|--------|----------|---------------------------------------------|

| 8 |        | RGJ      | 52Three phase power monitoring and analysis |

| 22 | WATT_A | 24 | 0x000000 | A-phase active power register (full wave |

|----|--------|----|----------|------------------------------------------|

| 22 | WAII_A | 24 | 0x000000 | and fundamental wave optional)           |

| 23 | WATT B | 24 | 0x000000 | B-phase active power register (full wave |

| 25 | WAII_D | 24 | 0x000000 | and fundamental wave optional)           |

| 24 | WATT C | 24 | 0x000000 | C-phase active power register (full wave |

| 24 | WAII_C | 24 | 0x000000 | and fundamental wave optional)           |

| 25 | WATT   | 24 | 0x000000 | Combined active power register (full     |

| 23 | WAII   | 24 | 0x000000 | wave and fundamental wave optional)      |

It can be set by the add\_sel register, the power sum is absolute value addition or algebraic sum addition.

| 0x98 | MODE3   | Operating mode register |                                                                                                                               |  |

|------|---------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|

| No.  | name    | default value           | description                                                                                                                   |  |

| [8]  | add_sel | 1'b0                    | watt and var conjoint sum accumulation method: 0-<br>absolute value addition,  a + b + c ; 1-algebraic sum<br>addition, a+b+c |  |

Note: If four-quadrant reactive energy is required, MODE3[8] needs to be set to 1;

### 3.2.2 Active power calibration

Contains three 16-bit active power offset correction registers WATTOS\_A/B/C and three 16-bit active power gain correction registers WATTGN\_A/B/C, the default value is 0x0000.

These registers can be used for digital calibration or error pre-calibration before leaving the factory.

WATTOS is used to eliminate the DC deviation in the active power calculation, and WATTGN is used to eliminate the gain deviation in the active power calculation. The deviation here may be due to the crosstalk between the two channels generated on the PCB board and the integrated circuit itself in the power calculation, or it may be the gain deviation of the ADC channel itself.

Deviation correction can make the value in the active power register close to 0 under no load.

| Address | Name     | Bit width | Defaults | Description                                               |

|---------|----------|-----------|----------|-----------------------------------------------------------|

| B6      | WATTGN_A | 16        | 0x0000   | A-phase active power gain adjustment register, complement |

Shanghai Belling Co., Ltd.

| D7 | 16 | 00000 | B-phase active power gain adjustment                 |

|----|----|-------|------------------------------------------------------|

| 6  |    | BIG.  | <b>552</b> Three phase power monitoring and analysis |

| B7 | WATTGN_B    | 16 | 0x0000 | B-phase active power gain adjustment register, complement |

|----|-------------|----|--------|-----------------------------------------------------------|

| B8 | WATTGN_C    | 16 | 0x0000 | C-phase active power gain adjustment                      |

|    |             |    |        | register, complement                                      |

| C2 | WATTOS A    | 16 | 0x0000 | A-phase active power bias adjustment                      |

| 02 | w/////05_// | 10 | 0,0000 | register, complement                                      |

| C3 | WATTOS B    | 16 | 0x0000 | B-phase active power bias adjustment                      |

| CS | WATIO5_D    | 10 | 0X0000 | register, complement                                      |

| C4 | WATTOS C    | 16 | 0x0000 | C-phase active power bias adjustment                      |

| C4 | WATTOS_C    | 10 | 0x0000 | register, complement                                      |

For details of the correction formula, please refer to the register detailed description chapter.

### 3.2.3 Active power anti-creeping

It has a patented power anti-submarine function to ensure that the power output is 0 when there is no current input. Active anti-creep threshold register (WA\_CREEP), a 12-bit unsigned number, the default is 0x04C. This value is internally expanded by 1 and compared with the absolute value of the input active power signal. When the absolute value of the input active power signal is less than this value, the output active power is set to zero. This can make the value of the output to the active power register 0 under no load, even if there is a small noise signal.

| Address | Name                   | Bit width | Defaults | Description                                                                                                                                                          |

|---------|------------------------|-----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 88      | VAR_CREEP/<br>WA_CREEP | 24        | 0x04C04C | <ul><li>[23:12] is the reactive anti-creeping</li><li>power threshold register</li><li>[11:0] is the active anti-creeping power</li><li>threshold register</li></ul> |

Corresponding to CREEP value =  $\frac{Corresponding power register value}{2}$

The WA\_CREEP can be set according to the WATT value of the power register, and their corresponding relationship, the default anti-submarine value is about 20 parts per million of the power full scale.

When a phase is in the anti-submarine state, the power of the phase below the threshold does not participate in the energy accumulation.

The combined active anti-creep threshold register (WA\_CREEP2) is a 12-bit unsigned number, and the default is 00H. This value is internally expanded by 1 and

compared with the absolute value of the input combined active power signal. When the absolute value of the input combined active power signal is less than this value, the output combined active power is set to zero. This is used to prevent creeping of the combined power.

| Address | Name                     | Bit width | Defaults | Description                                                                                                                                                                                               |

|---------|--------------------------|-----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 89      | VAR_CREEP2/<br>WA_CREEP2 | 24        | 0x000000 | <ul><li>[23:12] is the combined reactive anti-<br/>creeping power threshold register</li><li>VAR_CREEP2;</li><li>[11:0] is the combined active anti-<br/>creeping threshold register WA_CREEP 2</li></ul> |

### 3.2.4 Active power small signal compensation

For the calculation of active power, in order to reduce the noise error in the small signal section, you can pass to the small signal compensation register to adjust the non-linear error of the small signal section.

| Address | Name     | Bit width | Defaults | Description                                 |

|---------|----------|-----------|----------|---------------------------------------------|

|         |          | 2.1       | 0.000    | [23:12] Corresponding to active power small |

| 82      | WA_LOS_A | 24        | 0x000    | signal compensation register, complement.   |

|         |          |           | 0.000    | [23:12] Corresponding to active power small |

| 83      | WA_LOS_B | 24        | 0x000    | signal compensation register, complement.   |

| 0.4     |          |           | 0.000    | [23:12] Corresponding to active power small |

| 84      | WA_LOS_C | 24        | 0x000    | signal compensation register, complement.   |

## 3.2.5 Active power selection

Active power calculation method, you can select fundamental active power or full-wave active power through watt\_sel, and the default is full-wave active power.

| 0x98 | MODE3    | Operating mode register |                                                          |  |

|------|----------|-------------------------|----------------------------------------------------------|--|

| No.  | name     | default value           | description                                              |  |

| [17] | watt_sel | 1'b0                    | Watt waveform selection: 0-full wave, 1-fundamental wave |  |

Provide three-phase electric energy pulse accumulation. The principle is that the active power of each phase can be integrated for a period of time to obtain the functional energy during this period, and further convert the energy into the corresponding frequency check pulse CF. The more electricity is used, the CF frequency will be faster, and the less electricity will be slow. Active energy accumulation includes positive power accumulation, negative power accumulation, algebraic and/absolute value accumulation.

**B6552**Three phase power monitoring and analysis

### 3.3.1 Active energy output

BELLING

The energy (power consumption) can be obtained by counting the CF pulse, which is stored in the Nth phase energy accumulation register CF[N]\_CNT and the total energy register CF\_CNT, as shown in the figure below.

| Address | Name      | Bit width | Defaults | Description                                          |

|---------|-----------|-----------|----------|------------------------------------------------------|

| 2F      | CF_A_CNT  | 24        | 0x000000 | A-phase active pulse count, unsigned                 |

| 30      | CF_B_CNT  | 24        | 0x000000 | B-phase active pulse count, unsigned                 |

| 31      | CF_C_CNT  | 24        | 0x000000 | C-phase active pulse count, unsigned                 |

| 32      | CF_CNT    | 24        | 0x000000 | Combined phase active pulse count, unsigned          |

| 33      | CFP_A_CNT | 24        | 0x000000 | A-phase positive active pulse count,<br>unsigned     |

| 34      | CFP_B_CNT | 24        | 0x000000 | B-phase positive active pulse count,<br>unsigned     |

| 35      | CFP_C_CNT | 24        | 0x000000 | C-phase positive active pulse count,<br>unsigned     |

| 36      | CFP_CNT   | 24        | 0x000000 | Combined phase positive active pulse count, unsigned |

| 37      | CFN_A_CNT | 24        | 0x000000 | A-phase negative active pulse count,<br>unsigned     |

| 38      | CFN_B_CNT | 24        | 0x000000 | B-phase negative active pulse count,<br>unsigned     |

| 39      | CFN_C_CNT | 24        | 0x000000 | C-phase negative active pulse count,<br>unsigned     |

| 3A      | CFN_CNT   | 24        | 0x000000 | Combined phase negative active pulse count, unsigned |

### 3.3.2 Active energy pulse output selection

| 0x98 | MODE3     | Operating mode register |                                    |  |

|------|-----------|-------------------------|------------------------------------|--|

| No.  | name      | default description     |                                    |  |

| [9]  | cf_enable | 1'b0                    | 0-cf disable, default; 1-cf enable |  |

|         | <b>BL6552</b> Three phase power monitoring and analysis |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|---------|---------------------------------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| [13:10] | CF_SEL                                                  | 4'b0000 | Channel CF1/CF2 output selection, Default 0000, turn off<br>CF1/CF2; 1111, turn off CF; 0001,watt_a/var_a electric<br>energy CF; 0010,watt_b/var_b electric energy CF; 0011,<br>watt_c/var_c electric energy CF; 0100, watt/var electric<br>energy CF; 0101,watt_p_a/var1 electric energy CF;<br>0110,watt_p_b/var2 electric energy CF; 0111,watt_p_c/var3<br>electric energy CF; 1000,watt_p/var4 electric energy CF;<br>1001,watt_n_a/va_a electric energy CF; 1010,watt_n_/va_b<br>electric energy CF; 1011,watt_n_c/va_c electric energy CF;<br>1100,watt_n/va electric energy CF 1101, (same as 0100);<br>1110, apparent energy CF; |  |  |

| [15]    | cf_add_sel                                              | 1'b0    | watt and var energy addition methods: 0-absolute value<br>addition; 1-algebra and addition (phase separation and<br>combination)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

···· /

First set MODE3[9]=1 to select the CF pin to output electric energy pulses, and then set CF SEL to select the corresponding electric energy pulses.

CF\_add\_sel is used to set the accumulating method of combined phase electric energy and split phase electric energy: algebraic sum or absolute value addition.

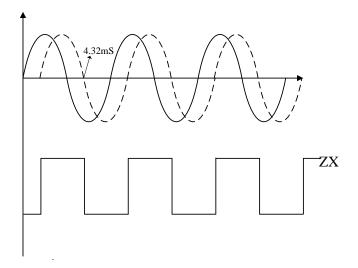

The count results of CF pulses are stored in the CF\*\_\*\_CNT registers, and the number of pulses can also be counted directly from the CF pin through I/O interrupts. When the cycle of CF is less than 180ms, it is a pulse with a 50% duty cycle. , When it is greater than or equal to 180ms, the pulse width is fixed to 90ms.

### 3.3.3 Active energy pulse output ratio

In the energy accumulation, the speed of energy accumulation can be set through the CF\_DIV register, each gear \*2 times relationship, a total of 12 gears.

| Address | Name  | Bit width | Defaults | Description                       |

|---------|-------|-----------|----------|-----------------------------------|

| CE      | CFDIV | 12        | 0x010    | Active CF scaling register [11:0] |

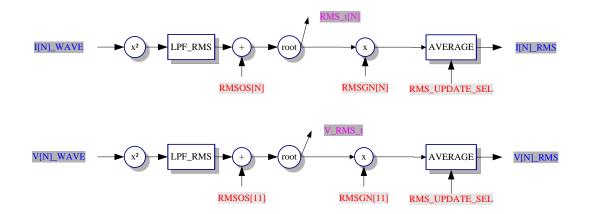

# 3.4 Calculation principle of the effective value of current and voltage

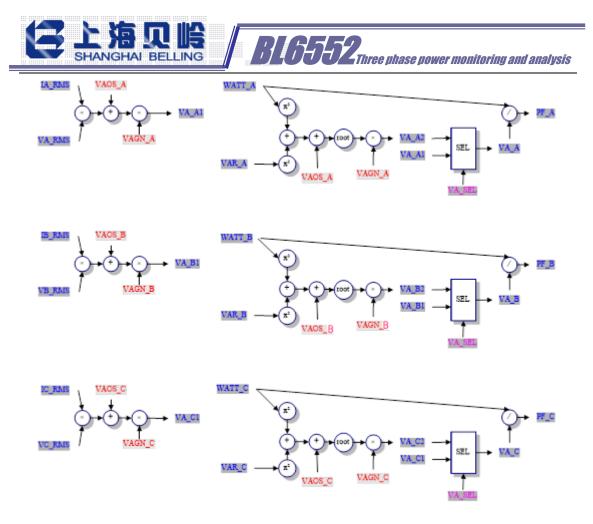

The calculation principle of the effective value of the channel, as shown in the figure below

The original waveform of each channel passes through the square circuit ( $X^2$ ), the effective value low-pass filter (LPF\_RMS), and the root circuit (ROOT) to obtain the instantaneous value RMS\_t of the effective value, and then average the average value of each channel The values I[N]RMS and V[N]\_RMS.

### 3.4.1 Effective value output

The effective value calculation result is output and sum to 7 registers

| Address | Name   | Bit width | Defaults | Description                                 |

|---------|--------|-----------|----------|---------------------------------------------|

| D       | IC_RMS | 24        | 0x000000 | C-phase current RMS register, unsigned      |

| Е       | IB_RMS | 24        | 0x000000 | B-phase current RMS register, unsigned      |

| F       | IA_RMS | 24        | 0x000000 | A-phase current RMS register, unsigned      |

| 10      | IN_RMS | 24        | 0x000000 | Zero wire current RMS register,<br>unsigned |

| 13      | VA_RMS | 24        | 0x000000 | A-phase voltage RMS register, unsigned      |

| 14      | VB_RMS | 24        | 0x000000 | B-phase voltage RMS register, unsigned      |

| <b>BIG552</b> Three phase power monitoring and analy |  |  |  |  |  |

|------------------------------------------------------|--|--|--|--|--|

|                                                      |  |  |  |  |  |

For the conversion formula of voltage RMS and current RMS, please refer to the detailed description chapter of the register.

### 3.4.2 Setting of effective value input signal

Set MODE2[21:0].WAVE\_RMS\_SEL to select the effective value to calculate the input waveform. Each channel can be selected by two bits, 00-high pass, 01-select fundamental wave, 11-select sinc for direct output.

| 0x97   | MODE2        |               | Operating mode register                                                                                                                                                                                                                                                                   |

|--------|--------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No.    | name         | default value | description                                                                                                                                                                                                                                                                               |

| [21:0] | WAVE_RMS_SEL | 11{2'b00}     | RMS waveform selection, 00-high pass, 01-<br>select fundamental wave, 11-select sinc<br>output [3,2]: C-phase current; [5,4]: B-phase<br>current [7,6]: Phase A current; [9:8]: Neutral<br>line current [15,14]: Phase A voltage;<br>[17,16]: Phase B voltage [19,18]: Phase C<br>voltage |

## 3.4.3 Valid value refresh rate setting

Set MODE2[22].RMS\_UPDATE\_SEL, you can choose the effective value

average refresh time is 525ms or 1050ms, the default is 525ms.

| 0x97 | MODE2          | Operating mode register |                                                                                                           |  |

|------|----------------|-------------------------|-----------------------------------------------------------------------------------------------------------|--|

| No.  | name           | default value           | description                                                                                               |  |

| [22] | RMS_UPDATE_SEL | 1'b0                    | Valid value register update speed selection,<br>1 is 1050ms, 0 is 525ms, 525ms is selected<br>by default; |  |

### 3.4.4 Current and voltage RMS calibration

Contains 7 24-bit RMS offset correction registers RMSOS[N] and 7 16-bit RMS gain correction registers RMSGN[N], the default value is 0x0000.

They use data in the form of 2's complement to calibrate the deviation in the effective value calculation. This deviation may come from input noise, because there

is a step of square operation in calculating the effective value, which may introduce a DC offset caused by noise. Gain and offset correction can make the value in the

effective value register close to 0 under no load.

**BL6552**Three phase power monitoring and analysis

Name Bit width Address Defaults Description Current C channel RMS gain adjustment 0x0000 6D IC\_RMSGN 16 register Current B channel RMS gain adjustment 6E IB\_RMSGN 16 0x0000 register Current A channel RMS gain adjustment 0x0000 6F IA\_RMSGN 16 register Current N channel RMS gain adjustment 70 IN RMSGN 16 0x0000 register Voltage A channel RMS gain adjustment 73 VA RMSGN 0x0000 16 register Voltage B channel RMS gain adjustment 74 VB\_RMSGN 16 0x0000 register Voltage C channel RMS gain adjustment VC RMSGN 0x0000 75 16 register Current C channel RMS offset correction 0x000000 78 IC RMSOS 24 register Current B channel RMS offset correction 0x000000 79 **IB\_RMSOS** 24 register Current A channel RMS offset correction 7A IA\_RMSOS 24 0x000000 register Current N channel RMS offset correction 0x000000 7**B** IN\_RMSOS 24 register Voltage A channel RMS offset correction 7E VA\_RMSOS 24 0x000000 register Voltage B channel RMS offset correction VB\_RMSOS 0x000000 7F 24 register Voltage C channel RMS offset correction 0x000000 80 VC\_RMSOS 24 register

For details of the calibration formula, please refer to the register detailed description chapter.

### 3.4.5 Effective value of anti-creeping

It has a patented effective value anti-submarine function to ensure that the effective value output is 0 when there is no current input.

BIG552 Three phase power monitoring and analysis

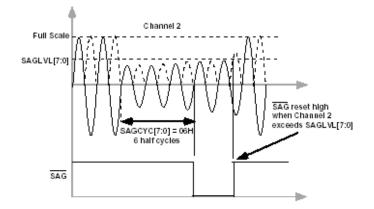

The effective value anti-creep threshold register (RMS\_CREEP) is a 12-bit unsigned number, and the default value is 0x200. This value is internally expanded by 1 and compared with the absolute value of the input effective value signal. When the input effective value signal is less than this value, the output effective value is set to zero. This can make the value output to the effective value register 0 even if there is a small noise signal under no load.

| Address | Name                     | Bit width | Defaults | Description                                                                                                                                        |

|---------|--------------------------|-----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 8A      | REVP_CREEP/<br>RMS_CREEP | 24        | 0x04C200 | [23:12] is the reverse indication threshold<br>register REVP_CREEP; [11:0] is the<br>effective value small signal threshold<br>register RMS_CREEP; |

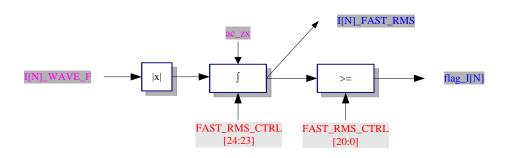

# 3.5 Fast RMS detection principle

Fast RMS calculation principle see below,

7 channels have fast effective value registers, which can detect half cycle or cycle effective value. This function can be used for overcurrent detection.

The input waveform is obtained by taking the absolute value and then integrating within the specified time to obtain a fast effective value.

### 3.5.1 Fast RMS output

Fast RMS output register shown below channel 7

| Address | Name        | Bit width | Defaults | Description                                   |

|---------|-------------|-----------|----------|-----------------------------------------------|

| 18      | IC_FAST_RMS | 24        | 0x000000 | C-phase current rapidly RMS register unsigned |

| <b>BIG552</b> Three phase power monitoring and analysis |

|---------------------------------------------------------|

|---------------------------------------------------------|

| 19 | IB_FAST_RMS | 24 | 0x000000 | B-phase current rapidly RMS register unsigned |

|----|-------------|----|----------|-----------------------------------------------|

| 1A | IA_FAST_RMS | 24 | 0x000000 | A-phase current rapidly RMS register unsigned |

| 1B | IN_FAST_RMS | 24 | 0x000000 | Neutral current rapidly RMS register unsigned |

| 1E | VA_FAST_RMS | 24 | 0x000000 | A-phase voltage rapidly RMS register unsigned |

| 1F | VB_FAST_RMS | 24 | 0x000000 | B-phase voltage rapidly RMS register unsigned |

| 20 | VC_FAST_RMS | 24 | 0x000000 | C-phase voltage rapidly RMS register unsigned |

### 3.5.2 Fast RMS input selection

Referring to a block diagram of the waveform of the source waveform channel.

| 0x96 | MODE1   | Operating mode register   |                                                                                                           |  |  |

|------|---------|---------------------------|-----------------------------------------------------------------------------------------------------------|--|--|

| No.  | name    | default value description |                                                                                                           |  |  |

| [22] | L_F_SEL | 1'b0                      | Over current select through high pass, the default is 0 to select no high pass, and 1 to select high pass |  |  |

You can choose to pass HPF and not pass HPF.

### 3.5.3 Fast RMS cumulative time

Computing fast RMS, to take the absolute value, and a good set according to the cumulative time integral. Generally, it is an integer multiple of half cycle and cycle time.

| Address | Name          | Bit width | Defaults | Description                                                                                                                                        |

|---------|---------------|-----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 8B      | FAST_RMS_CTRL | 24        | 0x20FFFF | [23:21] Channel fast effective value<br>register refresh time, half cycle and N<br>cycle can be selected, the default is<br>cycle; [20:0] reserved |

Choose cumulative time by FAST\_RMS\_CTRL[23:21], which can be divided into six types: 000-10ms, 001-20ms, 010-40ms, 011-80ms, 100-160ms, 101-320ms. By default, the cycle cumulative response time is 20ms, and the cumulative time is selected. The longer the beating, the smaller the beating.

SHANGHAL BELLING BL6552 Three phase power monitoring and analysis

### 3.5.4 Grid frequency selection

In addition, it is necessary to distinguish between 50Hz and 60Hz half cycle time

### (AC\_FREQ\_SEL).

| 0x97 | MODE2       | Operating mode register   |                                                                           |  |  |

|------|-------------|---------------------------|---------------------------------------------------------------------------|--|--|

| No.  | name        | default value description |                                                                           |  |  |

| [23] | AC_FREQ_SEL | 1'b0                      | AC frequency selection, 1 is 60Hz, 0 is 50Hz, 50Hz is selected by default |  |  |

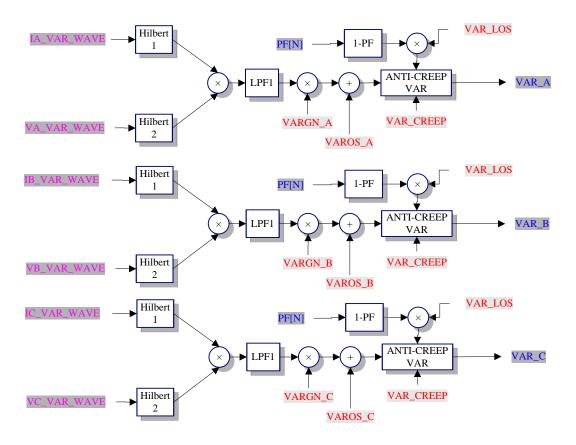

# 3.6 Reactive power calculation

The principle of reactive power calculation is shown in the figure below

After the current and voltage waveforms of each phase pass through the Hilbert filter, digital multiplication is performed, and then the reactive power signal can be obtained after the low-pass filter, gain and deviation calibration, anti-creeping judgment and averaging processing in order. After integration, the reactive energy pulse accumulation is obtained.

## 3.6.1 Reactive phase compensation

At the ADC output position, a digital calibration method for small phase errors is provided. It can introduce a small time delay or lead into the signal processing circuit to compensate for small phase errors. Since this compensation needs to be timely, this method is only suitable for small phase errors in the range of  $<0.6^{\circ}$ . Using time-shift technology to correct large phase errors will introduce significant phase errors in higher harmonics.

Regarding the current and voltage signals for reactive power calculation, each is adjusted by a 4-bit register:

| Address | Name        | Bit width | Defaults | Description                                                                                                                                                                                                                                                                                                                                                                        |

|---------|-------------|-----------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6A      | VAR_PHCAL_I | 15        | 0x0000   | Reactive power phase correction (fine<br>tuning): [3:0] bits fine-tune the phase of<br>the A-phase current channel in the reactive<br>power calculation; [7:4] bits fine-tune the<br>phase of the B-phase current channel in<br>the reactive power calculation; [11:8] Bit<br>to fine-tune the phase of the C-phase<br>current channel in the reactive power<br>calculation;       |

| 6B      | VAR_PHCAL_V | 15        | 0x0000   | Reactive power phase correction (fine<br>adjustment): [3:0] bits fine-tune the phase<br>of the A-phase voltage channel in the<br>reactive power calculation; [7:4] bits fine-<br>tune the phase of the B-phase voltage<br>channel in the reactive power calculation;<br>[11:8] Bit to fine-tune the phase of the C-<br>phase voltage channel in the reactive<br>power calculation; |

### 3.6.2 Reactive power output

Output 3 phase and combined phase reactive power, fundamental wave and full wave reactive power are given at the same time

| Address | Name    | Bit width | Defaults | Descripti | on    |       |          |       |

|---------|---------|-----------|----------|-----------|-------|-------|----------|-------|

| 5A      | VAR A   | 24        | 0x000000 | A-phase   | (full | wave) | reactive | power |

| 511     | V/MC_/Y | 27        | 0,000000 | register  |       |       |          |       |

Shanghai Belling Co., Ltd.

| 8  |        |    | BIG5     | <b>52</b> Three phase power monitoring and analysis          |

|----|--------|----|----------|--------------------------------------------------------------|

| 5B | VAR_B  | 24 | 0x000000 | B-phase (full wave) reactive power register                  |

| 5C | VAR_C  | 24 | 0x000000 | C-phase (full wave) reactive power register                  |

| 5D | VAR    | 24 | 0x000000 | Combined phase (full wave) reactive power register           |

| 2A | FVAR_A | 24 | 0x000000 | A-phase (fundamental wave) reactive power register           |

| 2B | FVAR_B | 24 | 0x000000 | B-phase (fundamental wave) reactive power register           |

| 2C | FVAR_C | 24 | 0x000000 | C-phase (fundamental wave) reactive power register           |

| 2D | FVAR   | 24 | 0x000000 | Combined phase (fundamental wave)<br>reactive power register |

### 3.6.3 Reactive power calibration

Contains three 16-bit reactive power offset correction registers VAROS and three 16-bit reactive power gain correction registers VARGN, the default value is 0x0000.

Contains three 16-bit fundamental reactive power offset correction registers FVAROS and three 16-bit fundamental reactive gain correction registers FVARGN, the default value is 0x0000.

These registers can be used for digital calibration or error pre-calibration before leaving the factory.